## CY15FRAMKIT-002

# Excelon<sup>TM</sup> Ultra QSPI F-RAM Development Kit User Guide

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709 www.cypress.com

© Cypress Semiconductor Corporation, 2018. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

# Contents

| 1.  | Introduction  |                                                 |    |

|-----|---------------|-------------------------------------------------|----|

|     | 1.1           | Kit Contents                                    | 4  |

|     | 1.2           | Getting Started                                 | 4  |

|     | 1.3           | Pre-requisite software                          | 4  |

|     | 1.4           | Pre-requisite Hardware                          | 4  |

|     | 1.5           | Additional Resources                            | 4  |

| 2.  | Kit C         | Overview                                        | 5  |

|     | 2.1           | CY15FRAMKIT-002 Kit Overview                    | 5  |

|     | 2.2           | Kit Introduction and Configuration Guide        | 6  |

|     | 2.3           | F-RAM and MCU Kit Connection                    | 10 |

| 3.  | Kit Operation |                                                 |    |

|     | 3.1           | Programming the NUCLEO-433LC-P evaluation board | 11 |

|     | 3.2           | Quad SPI Configuration for STM32L433RC          | 17 |

| 4.  | Firm          | nware Details                                   | 20 |

| Α.  | App           | endix                                           | 23 |

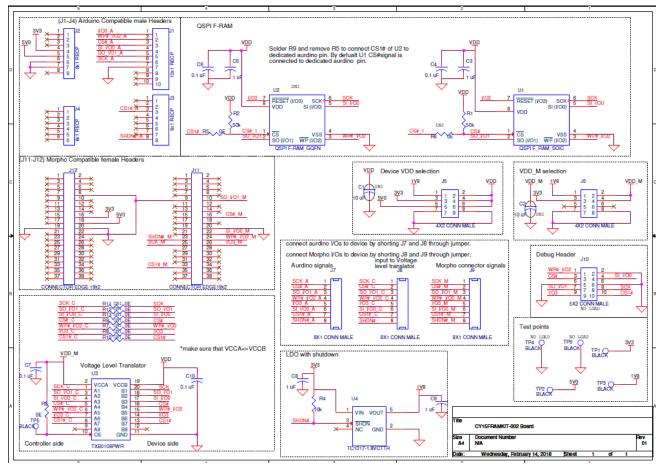

|     | A.1           | CY15FRAMKIT-002 Kit Block Diagram               | 23 |

|     | A.2           | CY15FRAMKIT-002 Kit Components Placement        | 24 |

|     | A.3           | CY15FRAMKIT-002 Kit Schematic                   | 25 |

|     | A.4           | Pin Assignment Table                            | 25 |

|     | A.5           | Use of Zero-ohm Resistors and No Load           |    |

|     | A.6           | Bill of Materials (BOM)                         | 29 |

|     | A.7           | CY15FRAMKIT-002 Board - Jumper Details          | 30 |

| В.  | App           | 31                                              |    |

|     | B.1           | GUI Menu                                        | 31 |

| Rev | ision         | History                                         | 34 |

|     | Doci          | ument Revision History                          | 34 |

|     |               |                                                 |    |

## 1. Introduction

Thank you for your interest in the CY15FRAMKIT-002 FRA-M Kit (DVK). The kit (shield) is designed as an easy-to-use and inexpensive development kit as well as evaluation platform for Cypress's latest Quad SPI enabled Serial F-RAM. This kit works in conjunction with the NUCLEO-L433RC-P MCU Evaluation Board, a starter kit for ARM® Cortex®-M4-based ST Microelectronics devices. You will need both kits to demonstrate the operation described in this guide. This board features a 4-Mbit Quad SPI F-RAM, associated circuit, Arduino as well as Morpho connectivity. This kit supports 3.3-V or 1.8V power supply.

#### 1.1 Kit Contents

The CY15FRAMKIT-002 Kit includes following contents,

- CY15FRAMKIT-002 DVK board with CY15B104QSN-108SXI. 108-MHz 4-Mbit Quad SPI F-RAM

- Quick Start Guide

#### 1.2 Getting Started

This guide helps you to get acquainted with the CY15FRAMKIT-002 DVK. The Kit Installation chapter on page 10 describes the software required to utilize the driver set provided for this kit. The Kit Overview chapter on page 14 explains the features of the kit. The Kit Operation chapter on page 20 explains how to program and run the kit. The Kit Software chapter on page 32 explains the GUI to test out the QSPI F-RAM features. The Kit Example Firmware chapter on page 41 explains the F-RAM access APIs and a link to download the test project. The Appendix on page 23 provides the kit block diagram, schematics, pin assignment, and the bill of materials (BOM)

## 1.3 Pre-requisite software

- Keil uVision 5 software (for development and programming)

- STSW-LINK009 ST-LINK, ST-LINK/V2, ST-LINK/V2-1 USB driver signed for Windows7, Windows8, Windows10

- STSW-LINK007 ST-LINK, ST-LINK/V2, ST-LINK/V2-1 firmware upgrade

### 1.4 Pre-requisite Hardware

- NUCLEO-L433RC-P: STM32 Nucleo64 Evaluation Board (details)

- CY15FRAMKIT-002 DVK board

#### 1.5 Additional Resources

- Details about the ST Micro-electronics Kit can be found here

- Details about Keil µVision installation can be found here (Download MDK-Arm tool chain)

- The test project and driver files are part of the compressed folder downloaded from Cypress community

- The datasheet for Cypress Quad SPI F-RAM mounted on the kit can be downloaded from here

## 2. Kit Overview

#### 2.1 CY15FRAMKIT-002 Kit Overview

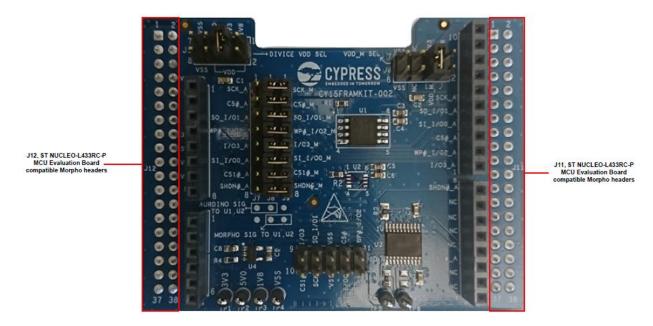

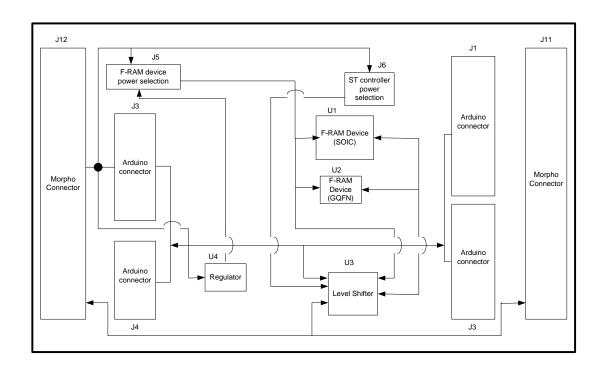

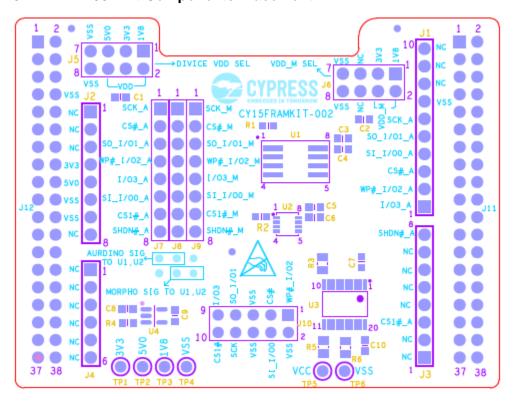

The CY15FRAMKIT-002 can be used to understand the features of the serial F-RAMs (SPI and QSPI). The DVK is an add-on board, which contains a 4-Mbit Excelon<sup>TM</sup> -Ultra QSPI F-RAM. It has four connectors that are Arduino UNO-compatible and connect to either ST NUCLEO-L433RC-P MCU Evaluation Board or Arduino UNO R3 board for SPI evaluation. It also provides two 19x2 Morpho headers (J11 and J12) compatible with an ST NUCLEO-L433RC-P MCU Evaluation Board for QSPI evaluation. The kit operates using a 1.8-V/3.3-V power supply from the baseboard. The CY15FRAMKIT-002 Kit consists of the following blocks as shown in Figure 1.

- 4-Mbit (512Kx8), Excelon<sup>™</sup> -Ultra Quad SPI F-RAM

- ST NUCLEO-L433RC-P MCU Evaluation Board compatible Morpho headers (J11, J12)

- Arduino Compatible I/O Header (J1, J2, J3, J4)

- Headers (J7, J8, J9) to select Arduino or Morpho connector signal connectivity to F-RAM device

- J6 header for 3.3-V/5.0-V F-RAM device VCC power supply selection

- J5 header for 1.8-V/3.3-V/5.0-V ST controller VCC power supply

- J10 debug header for probing the SPI/QSPI signals

- Test points for supported voltage (3V3/5V0/1V8) and ground signals (VSS)

- Do Not Install (DNI) footprint for the Excelon<sup>TM</sup> -Ultra Quad SPI F-RAM in 8-pin Grid-Array Quad Flat No-Lead

- GQFN package

J5, F-RAM Device VDD 4-Mbit (512Kx8), Excelon™ -Ultra Quad SPI F-RAM, SOIC J1, Arduino Compatible I/O Header . J2, Arduino Compatible I/O Head CYPRESS 0 0 00 00 00 00 00 . J4, Arduino Compatible I/O Heade J3, Arduino Compatible I/O Heade 4-Mbit (512Kx8), Excelon™ -Ultra Quad SPI F-RAM, GQFN (DNI) Test points J10, Debug

Figure 1. CY15FRAMKIT-002 Board Markup

#### 2.2 Kit Introduction and Configuration Guide

The following sections describe various aspects of the kit hardware and the kit setup.

#### 2.2.1 F-RAM Device Power Supply Jumper

The CY15FRAMKIT-002 Board hardware operates at 1.8 V/3.3 V, selected through header J5, as shown in Figure 2. The factory default jumper setting is 3.3 V (short pins 3 and 4 of J5). User can short the pins 1 and 2 of J5 for 1.8 V selection.

#### **CAUTION**

- Do not power the CY15FRAMKIT-002 board through an external power source. The board is designed to be powered by the ST NUCLEO-L433RC-P MCU Evaluation base board.

- The CY15FRAMKIT-002 operates from 1.8 V to 3.6 V. Exceeding the maximum voltage limit (3.6 V) can damage the board.

Figure 2. F-RAM Device VDD Select Jumper

### 2.2.2 ST Controller Device Power Supply Jumper

The ST NUCLEO-L433RC-P MCU Evaluation Board hardware operates at 1.8 V/3.3 V, selected through header J6, as shown in Figure 3. The factory default jumper setting is 3.3 V (short pins 3 and 4 of J6). User can short the pins 1 and 2 of J6 for 1.8 V selection.

#### CAUTION

- Do not power the ST NUCLEO-L433RC-P MCU Evaluation board through an external power source. The board is designed to be powered by the Regulator output on the board.

- The ST NUCLEO-L433RC-P MCU Evaluation operates from 1.8 V to 3.6 V. Exceeding the maximum voltage limit (3.6 V) can damage the board.

Figure 3. ST Controller Device VDD\_M Select Jumper

#### 2.2.3 Excelon™ -Ultra Quad SPI F-RAM

Figure 4 shows the 4-Mbit (512Kx8), 3.3 V, Excelon™ -Ultra Quad SPI F-RAM part in the 8-pin SOIC package option.

Figure 4. Cypress Serial Quad SPI F-RAM Device on the Board

#### 2.2.4 Morpho Headers to ST NUCLEO-L433RC-P MCU Evaluation Board

Figure 5 shows the Morpho headers to the ST NUCLEO-L433RC-P MCU Evaluation Board for QSPI interface evaluation – J11 and J12. You can plug the CY15FRAMKIT-002 board onto the ST NUCLEO-L433RC-P MCU Evaluation Board through these connectors. For the schematic, refer to the Appendix on page 23.

Figure 5. Morpho Headers to ST NUCLEO-L433RC-P MCU Evaluation Board

#### 2.2.5 Arduino Headers to ST NUCLEO-L433RC-P MCU Evaluation Board

Figure 6 shows the Arduino headers to the ST NUCLEO-L433RC-P MCU Evaluation Board for SPI Interface evaluation – J1, J2, J3 and J4. You can plug the CY15FRAMKIT-002 board onto the ST NUCLEO-L433RC-P MCU Evaluation Board through these connectors. For the schematic, refer to the Appendix on page 23.

J1, Arduino Compatible I/O Header J2, Arduino Compatible I/O Hea 0 00 . CS# M .. 00 00 . 0 0 0 0 0 0 0 0 10 littilitie 0 0 0 0 0 0 ... 6 J4, Arduino Compatible I/O Header J3, Arduino Compatible I/O Header

Figure 6. Arduino Headers to ST NUCLEO-L433RC-P MCU Evaluation Board

#### 2.2.6 Headers to select Arduino or Morpho connector signal connectivity to F-RAM device

Figure 7 shows the headers – J7, J8 and J9. User can short F-RAM device signals to Arduino connector by shorting J7 and J8 or to Morpho connector by shorting J9 and J8 header through jumper. For the schematic, refer to the Appendix on page 23.

Headers (J7, J8, J9) to select Arduino or Morpho connector signal connectivity to F-RAM device

IVICE VDD

I C1

SCK

C59

/O1

S1-17

ON

S1-17

SHDN9

Figure 7. Headers to select Arduino or Morpho connector signals

#### 2.2.7 Debug Header

Debug header is provided for easy access to the Quad SPI F-RAM communication pins. As shown in Figure 8, header J10 provides access to the SPI F-RAM device communication signals. For the schematic, refer to the Appendix on page 23.

Figure 8. Debug Header

#### 2.2.8 Test Points

The CY15FRAMKIT-002 board provides 3V3, 5V0, 1V8, VSS, and VCC test points as shown in Figure 9. Test Points. These test points are loaded by default.

Figure 9. Test Points

Table 1. Test Points

| Test Points | Description                                           |  |

|-------------|-------------------------------------------------------|--|

| 3V3         | Test point for the kit board power supply             |  |

| 5V0         | Test point for the kit board power supply             |  |

| 1V8         | Test point for the kit board power supply             |  |

| VSS         | Test point for the kit board ground                   |  |

| VCC         | Test point for the F-RAM device (U1, U2) power supply |  |

**CAUTION**: The VCC test point is only for probing and measurement purposes. Do not power the kit using this test point to avoid any damage to the board.

#### 2.2.9 8-pin Grid-Array Quad Flat No-Lead GQFN package - Not Populated by Default

The CY15FRAMKIT-002 board provides a footprint option for the Excelon™ -Ultra Quad SPI F-RAM in 8-pin GQFN package. You can mount a 4-Mbit (512Kx8), Excelon™ -Ultra Quad SPI F-RAM device to evaluate the GQFN package in addition to the default 8-pin SOIC option on the CY15FRAMKIT-002 board. An independent chip select control is provided for the 8-pin GQFN package, which enable access to the second device on the board with an appropriate firmware modification.

Figure 10. 8-pin GQFN - Not Populated by Default

#### 2.3 F-RAM and MCU Kit Connection

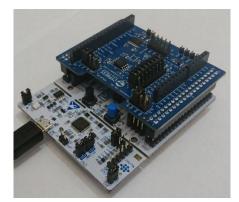

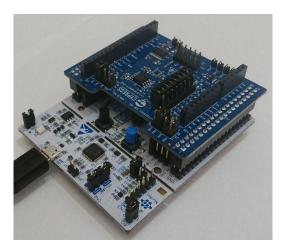

The ST MCU Evaluation Board is plugged onto the CY15FRAMKIT-002 through Arduino and Morpho connectors: Arduino (J1, J2, J3 and J4) and Morpho connectors (J11, J12), as shown in Figure 11. CY15FRAMKIT-002 mounted on ST MCU Evaluation Board.

Figure 11. CY15FRAMKIT-002 mounted on ST MCU Evaluation Board

**CAUTION:** The ST MCU Evaluation Board is plugged onto the CY15FRAMKIT-002 through its compatible headers J1, J2, J3, J4, J11 and J12. Because J11 and J12 are high pin-count connectors on the ST4 MCU Evaluation Board, removing the ST MCU Evaluation Board can be difficult and may lead to bending its J1, J2, J3, J4, J11 and J12 connector pins. Therefore, take care when removing the ST MCU Evaluation Board from the setup. Sliding the ST MCU Evaluation Board out of headers slowly and evenly will reduce the risk of bending connector pins.

## 3. Kit Operation

This section describes the setup needed to program the base board (NUCLEO-L433RC-P) to access the Quad SPI F-RAM on CY15FRAMKIT-002 DVK

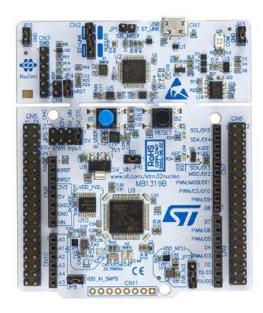

## 3.1 Programming the NUCLEO-433LC-P evaluation board

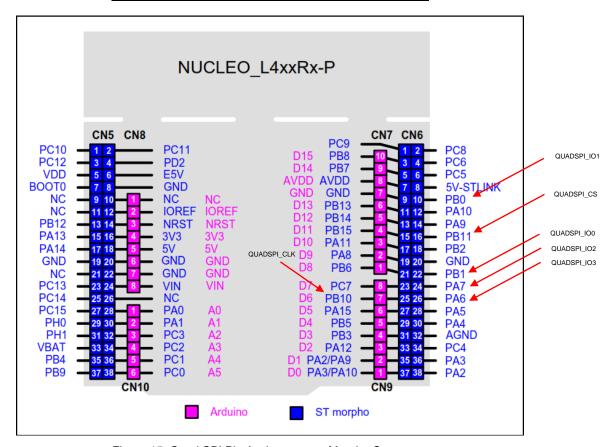

The NUCLEO-L433RC-P board is STM32 development board based on a Nucleo-64 platform. The board offers several features including an Arduino and Morpho connectivity. The controller is supported in a wide variety of Integrated Development Environments (IDEs) including IAR<sup>TM</sup>, Keil<sup>®</sup> and other GCC based IDEs for ARM<sup>TM</sup> architectures. Details about this platform can be found here

Figure 12: NUCLEO-L433RC-P Evaluation Board

The STM32L433RC MCU on the board supports an industry standard, high speed Quad SPI interface. This interface is routed on to the Morpho connectors of the NUCLEO board. The drivers and sample project has been written with STM32L433RC controller as target but can be easily modified to be compatible with any other ST microcontroller with Quad SPI interface. In firmware section of this document, appropriate sections will be highlighted to ensure compatibility with other ST microcontrollers.

#### 3.1.1 System Requirements

Before starting the user should:

- 1. Install the MDK-ARM v5.17 or later Integrated Development Environment (IDE) from Keil

- 2. ST-LINK/V2-1 driver will be installed automatically. In case of problem, the user can proceed with manual installation of the driver, from toolchains install directory

- 3. Download the STM32 Nucleo firmware from the www.st.com/stm32nucleo webpage.

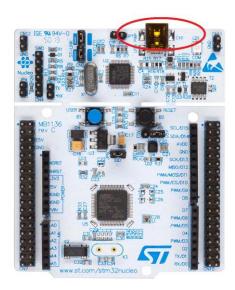

- 4. Establish the connection with the STM32 Nucleo board, by connecting CN1 of the Nucleo board to the USB port of the PC

- 5. Please refer to the guide here to resolve issues related to installation of Nucleo board drivers

Figure 13: Connector CN1 for Nucleo 64 board

#### 3.1.2 Compiling Test Project

This user guide is accompanied by a test project (Excelon\_QSPI.zip) that can be quickly compiled and programmed on to the Nucleo board to evaluate the Quad SPI F-RAM features

The folder Excelon\_QSPI contains a MDK-ARM project along with the required source/include files.

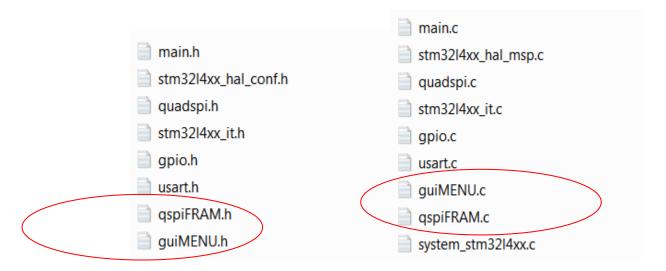

The Excelon\_QSPI/Inc and Excelon\_QSPI/Src folders contains header files critical for initializing the QSPI and LPUART modules of the ST controller. The function declarations for accessing Cypress's QSPI F-RAM are also provided in this folder

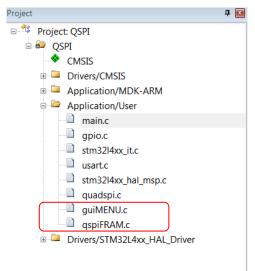

- 1. The files qspiFRAM(.h/.c) provide all the API accesses to the QSPI F-RAM device. User should include these (with appropriate code modification) in their project to access the QSPI F-RAM

- 2. The files guiMENU(.h/.c) are provided to allow evaluation of the F-RAM by sending commands over UART terminal (115200 bps, 8-NoParity-1). These files need not be included in the final project

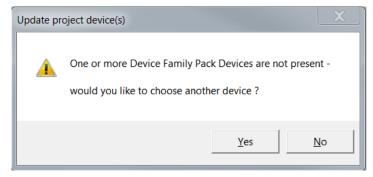

- 3. Open the uVision project in MDK-ARM folder. If the installer looks for Board support package, press ESC key (There is no native package for NUCLEO-L433RC-P board in Keil library)

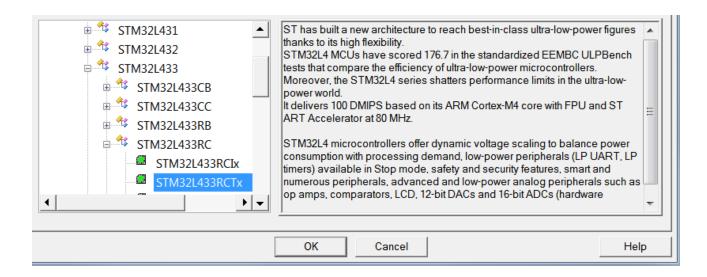

4. Click "Yes" on seeing this message and browse to the correct device (STM32L433RCTx) shown below

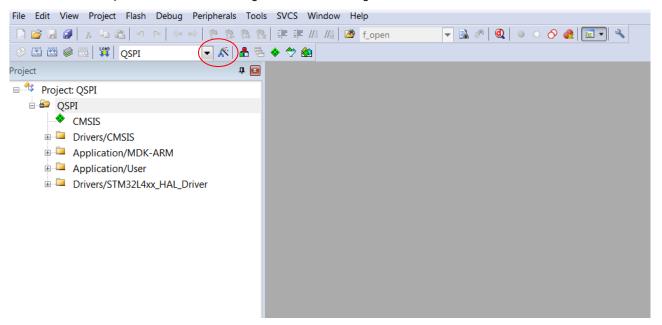

5. Your workspace should have following structure at this stage

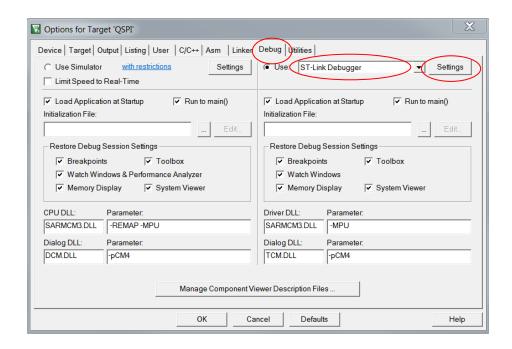

- 6. Before compiling, appropriate properties for target must be selected. Press "ALT+F7" or browse to "Options for Target" in "Project" menu

- 7. Update the clock speed to 80.00MHz in Target Xtal (MHz)

- 8. On "Debug" page, ST-Link Debugger should get populated automatically if the Nucleo board is plugged into USB port of the computer and the drivers are installed correctly

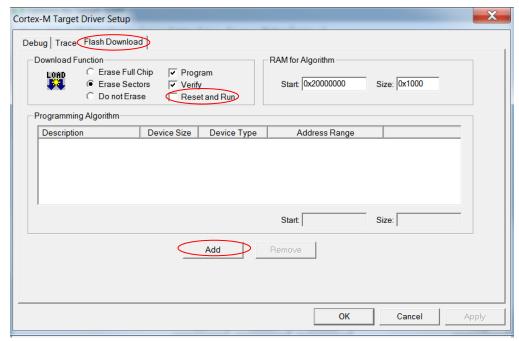

9. Click "Debugger – Settings" to select the appropriate Flash Programming Algorithm for this device

- 10. By default, there will be no Programming Algorithm on first time selection of this controller.

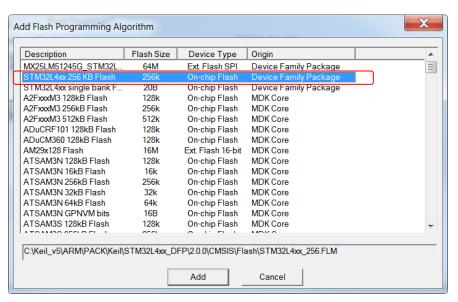

- 11. Click Add button to open a list of available algorithms.

- 12. The STM32L433RC MCU has 256Kbytes on On-Chip Flash. Select the appropriate programming algorithm

- 13. Click Add. Also "Check" the "Reset and Run" option on Target Driver Setup window to ensure that the device resets on successful program

- 14. Add qspiFRAM.c file in Application/User space. Also add guiFRAM.c file if you are evaluating the device features on HyperTerminal

15. Press F7 to build the project. There should be no errors or warning at this stage

```

linking...

Program Size: Code=23476 RO-data=1024 RW-data=20 ZI-data=9476

"QSPI\QSPI.axf" - 0 Error(s), 0 Warning(s).

Build Time Elapsed: 00:00:21

```

- 16. Press F8 to program the controller with default test program. Open a Hyper terminal program of your choice (puTTY, uCON etc) and establish a UART connection at 115200 bps with 8-bits message, no parity and 1 stop bit.

- 17. The controller will be waiting for appropriate GUI command. GUI commands will be explained in Appendix on page 32.

### 3.2 Quad SPI Configuration for STM32L433RC

The Arduino/Morpho QSPI F-RAM Kit is designed interface with both the SPI port on Arduino interface as well as the Quad SPI port on the Morpho interface. With help of jumper, user can select either of the interface. The drivers/API provided with test project are for initializing the Quad SPI port of controller only.

Figure 14: Complete Setup

#### 3.2.1 Quad SPI initialization

The initialization of Quad SPI block of ST controller is done by calling QUADSPI\_Init() function. The function is defined in "quadspi.c" but can be added to user's main application file for smaller project. QUADSPI\_Init() function initializes the "hgspi" structure.

hqspi.Instance = QUADSPI; hqspi.Init.ClockPrescaler = 32; hqspi.Init.FifoThreshold = 4; hqspi.Init.SampleShifting = QSPI\_SAMPLE\_SHIFTING\_NONE; hqspi.Init.FlashSize = 24; hqspi.Init.ChipSelectHighTime = QSPI\_CS\_HIGH\_TIME\_1\_CYCLE; hqspi.Init.ClockMode = QSPI\_CLOCK\_MODE\_0; hqspi.Init.FlashID = QSPI\_FLASH\_ID\_1; hqspi.Init.DualFlash = QSPI\_DUALFLASH\_DISABLE;

For details on Quad SPI interface of this controller, refer to AN4760 from STMicroelectronics. The critical variables for evaluating QSPI F-RAM are "ClockPrescaler" and "FlashSize"

**ClockPrescaler** = The default value in test project is 32. It corresponds to approximately 5MHz of clock frequency on QSPI interface. Users need to modify this variable for achieving the desired clock frequency. The Controller on the Nucleo board supports a maximum of 48MHz on Quad SPI Clock, while the Morpho connecter is expected to support up-to 30MHz.

Note: The limitation of clock speed is due to the low speed connectors used for design of Nucleo board as well as DVK kit. The Cypress F-RAM is capable of running at up to 108-MHz in Quad SPI mode.

"FlashSize" = The default value in test project is 24. The value corresponds to total number of address bits needed to address the memory attached to the interface. The Cypress F-RAM on the kit is a 4Mbit device but has 3-byte addressing. The default value of 24 can remain unchanged in user's application

#### 3.2.2 Quad SPI interface on STM32L433RC

The Quad SPI interface for this controller is routed to following GPIOs

| Sr. No.       | Quad SPI Interface Pin | STM32L433RC Pin |

|---------------|------------------------|-----------------|

| 1 QUADSPI_CS# |                        | PB11            |

| 2             | QUADSPI_CLK            | PB10            |

| 3 QUADSPI_IO0 |                        | PB1             |

| 4 QUADSPI_IO1 |                        | PB0             |

| 5 QUADSPI_IO2 |                        | PA7             |

| 6 QUADSPI_IO3 |                        | PA6             |

Figure 15: Quad SPI Pin Assignment on Morpho Connector

The CY15FRAMKIT-002 board plugs into the Nucleo board. Both Arduino and Morpho connectors need to be plugged in. The QSPI\_Init() function also ensures initialization of the controller pins as Quad SPI pins.

```

/**QUADSPI GPIO Configuration

PA6 ----> OUADSPI BK1 IO3

----> QUADSPI BK1 IO2

PA7

----> QUADSPI BK1 IO1

PB0

PB1

----> QUADSPI BK1 IO0

----> QUADSPI CLK

PB10

PB11

----> QUADSPI BK1 NCS

*/

GPIO InitStruct.Pin = GPIO PIN 6|GPIO PIN 7;

GPIO InitStruct.Mode = GPIO MODE AF PP;

GPIO InitStruct.Pull = GPIO PULLUP;

GPIO InitStruct.Speed = GPIO SPEED FREQ VERY HIGH;

GPIO InitStruct.Alternate = GPIO AF10 QUADSPI;

HAL GPIO Init(GPIOA, &GPIO InitStruct);

GPIO InitStruct.Pin = GPIO PIN 0|GPIO PIN 1|GPIO PIN 10|GPIO PIN 11;

GPIO InitStruct.Mode = GPIO MODE AF PP;

GPIO InitStruct.Pull = GPIO NOPULL;

GPIO InitStruct.Speed = GPIO SPEED FREQ VERY HIGH;

GPIO InitStruct.Alternate = GPIO AF10 QUADSPI;

HAL GPIO Init(GPIOB, &GPIO InitStruct);

```

Figure 16: Pin Initialization as Quad SPI

## 4. Firmware Details

This section summarizes the APIs written in qspiFRAM (.h/.c) file along with the uVision Example project provided by Cypress Semiconductors. Each function has been supplemented by user comments to help understand the usage. Revision 1.0 of this release covers limited features of the device. The detailed feature set of Cypress' Quad SPI F-RAM can be found in the device datasheet. The APIs listed here are for enabling easy usage of the Quad SPI F-RAM features and are not an official release of driver support from Cypress Semiconductors. Users are encouraged to leverage these APIs for building their end applications.

The Example project is stored in Excelon\_QSPI folder and has following structure:

| Project Files         | Description                        |

|-----------------------|------------------------------------|

| \Excelon_QSPI\MDK-ARM | Example project in uVISION 5       |

| \Excelon_QSPI\Inc     | Include files for Example project. |

| \Excelon_QSPI\Src     | Source files for Example project   |

| \Excelon_QSPI\Drivers | HAL Drivers for STM32              |

The QSPI F-RAM APIs are declared in \Excelon\_QSPI\Inc\qspiFRAM.h file and declared in \Excelon\_QSPI\Src\qspiFRAM.c. Following table provides summary of all the supported APIs for Revision 1.0 of this release. Unless specified explicitly the description is applicable only for the Quad SPI F-RAM device on the kit.

| Sr. No | API Name                                                                                                                                                                                                                                           | Description                                                                                                                         | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | bool FRAM_Interface_Reset (void)                                                                                                                                                                                                                   | This API resets the operating mode of the F-RAM device to SPI. All registers are reset to their default values                      | The F-RAM device can be configured in several operating modes (SPI, DPI or QPI) and can have several register settings. This API is written specifically to implement a "Go Home" feature in case the controller faces a miss-match of operating mode. For eg: during a sudden power cycle, the F-RAM device will retain its state but the controller will execute a power-up routine and will not be able to communicate with the F-RAM device. It is recommended to implement similar function in end application |

| 2      | void Read_Device_Status(void)                                                                                                                                                                                                                      | This API will read all the register values of the F-RAM device and stores it in run time structure variable                         | Assumes that Controller is in a known operating mode with respect to F-RAM                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3      | bool Read_ID(uint8_t IOMode, uint8_t Reg_lat)                                                                                                                                                                                                      | This API reads the ID register of the device and compares it with default value 0x50518206000000                                    | This function is utilized internally by FRAM_Interface_Reset (void) function.  Read_ID () API returns a success or a fail status based on whether the ID read from device matches the default value.  End user can leverage this API to identify the device operating mode (SPI, DPI or QPI)                                                                                                                                                                                                                        |

| 4      | Void FRAM_WREN(void)                                                                                                                                                                                                                               | Issues WREN (0x06) opcode to the device                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5      | Void FRAM_WRDI (void)                                                                                                                                                                                                                              | Issues WRDI (0x04) opcode to the device                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6      | void FRAM_RDSR1 (uint8_t *StatusReg);<br>void FRAM_RDSR2 (uint8_t *StatusReg);<br>void FRAM_RDCR1 (uint8_t *ConfigReg);<br>void FRAM_RDCR2 (uint8_t *ConfigReg);<br>void FRAM_RDCR4 (uint8_t *ConfigReg);<br>void FRAM_RDCR5 (uint8_t *ConfigReg); | These APIs can be used to read the status/Configuration registers of the F-RAM and store the register value in the pointer argument | The APIs assume that the F-RAM is in a known operating mode                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 7      | void FRAM_RDSN (void);<br>void FRAM_WRSN (uint8_t *SNreg);                                                                                                                                                                                         | These APIs can be used to read or write Serial Number Register                                                                      | SN Register is an 8-byte register. Read function will read the device's serial number and store it in SN_Reg array of operating_mode structure                                                                                                                                                                                                                                                                                                                                                                      |

| Sr. No | API Name                                                                                                                                                                                                                                                 | Description                                                                                                                                    | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |                                                                                                                                                                                                                                                          |                                                                                                                                                | The argument passed to Write function must be a pointer to an                                                                                                                                                                                                                                                                                                                                                                                     |

| 8      | bool FRAM_Write(uint32_t address, uint8_t *write_data, uint32_t write_length);                                                                                                                                                                           | This API performs write operation (Opcode 0x02) to the device                                                                                  | 8-byte array containing value of new Serial number  Device must be write enabled (FRAM_WREN()) prior to writing into the device.  This API performs write of length "write_length" bytes stored in array pointed by "*write_data", starting at location "address" in the F-RAM.  The API assumes that the controller is in a known operating                                                                                                      |

| 9      | bool FRAM_Fast_Write(uint32_t address, uint8_t *write_data, uint32_t write_length);                                                                                                                                                                      | This API performs Fast write operation (Opcode 0xDA) to the device                                                                             | mode (SPI, DPI or QPI)  Device must be write enabled (FRAM_WREN()) prior to writing into the device.  This API performs fast write of length "write_length" bytes stored in array pointed by "*write_data", starting at location "address" in the F-RAM.  The API assumes that the controller is in a known operating                                                                                                                             |

| 10     | bool FRAM_DIW(uint32_t address, uint8_t *write_data, uint32_t write_length);                                                                                                                                                                             | This API performs write operation to the device using                                                                                          | mode (SPI, DPI or QPI)  Device must be write enabled (FRAM_WREN()) prior to writing into the device.                                                                                                                                                                                                                                                                                                                                              |

| 11     | bool FRAM_DIOW(uint32_t address, uint8_t *write_data, uint32_t write_length);                                                                                                                                                                            | opcode 0xA2  This API performs write operation to the device using opcode 0xA1                                                                 | This API performs write of length "write_length" bytes stored in array pointed by "*write_data", starting at location "address" in the F-RAM.  The API assumes that the controller and the F-RAM device is in SPI operating mode                                                                                                                                                                                                                  |

| 12     | bool FRAM_QIW(uint32_t address, uint8_t<br>*write_data, uint32_t write_length);                                                                                                                                                                          | This API performs write operation to the device using opcode 0x32                                                                              | Device must be write enabled (FRAM_WREN()) prior to writing into the device.  This API performs write of length "write length" bytes stored in                                                                                                                                                                                                                                                                                                    |

| 13     | bool FRAM_QIOW(uint32_t address, uint8_t *write_data, uint32_t write_length);                                                                                                                                                                            | This API performs write operation to the device using opcode 0xD2                                                                              | array pointed by "*write_data", starting at location "address" in the F-RAM.  The API assumes that the controller and the F-RAM device is in SPI operating mode.  QUAD bit must be set prior to executing this API                                                                                                                                                                                                                                |

| 14     | bool FRAM_DDRWrite(uint32_t address, uint8_t *write_data, uint32_t write_length); bool FRAM_DDRQIOW(uint32_t address, uint8_t *write_data, uint32_t write_length); bool FRAM_DDRFastWrite(uint32_t address, uint8_t *write_data, uint32_t write_length); | This API is not tested for Revision 1.0 of this release                                                                                        | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 15     | bool FRAM_Read(uint32_t address,<br>uint8_t *read_data, uint32_t read_length);                                                                                                                                                                           | This API performs read operation (Opcode 0x03) to the device                                                                                   | This API performs read of length "read_length" bytes and stores it in array pointed by "*read_data", starting at location "address" in the controller.  The API assumes that the controller is in a known operating mode (SPI, DPI or QPI)                                                                                                                                                                                                        |

| 16     | bool FRAM_FastRead(uint32_t address, uint8_t *read_data, uint32_t read_length);                                                                                                                                                                          | This API performs read operation (Opcode 0x0B) to the device                                                                                   | This API performs fast read of length "read_length" bytes and stores it in array pointed by "*read_data", starting at location "address" in the controller.  The API assumes that the controller is in a known operating mode (SPI, DPI or QPI)                                                                                                                                                                                                   |

| 17     | bool FRAM_DORRead(uint32_t address, uint8_t *read_data, uint32_t read_length);                                                                                                                                                                           | This API performs read operation on the device using opcode 0x3B                                                                               | This API performs fast read of length "read_length" bytes and stores it in array pointed by "*read_data", starting at location "address" in the controller.                                                                                                                                                                                                                                                                                       |

| 18     | bool FRAM_DIORRead(uint32_t address, uint8_t *read_data, uint32_t read_length);                                                                                                                                                                          | This API performs read operation on the device using opcode 0xBB                                                                               | The API assumes that the controller and the F-RAM is in SPI<br>Operating mode                                                                                                                                                                                                                                                                                                                                                                     |

| 19     | bool FRAM_QORRead(uint32_t address, uint8_t *read_data, uint32_t read_length);                                                                                                                                                                           | This API performs read operation on the device using opcode 0x6B                                                                               | This API performs fast read of length "read_length" bytes and stores it in array pointed by "*read_data", starting at location "address" in the controller.                                                                                                                                                                                                                                                                                       |

| 20     | bool FRAM_QIORRead(uint32_t address, uint8_t *read_data, uint32_t read_length);                                                                                                                                                                          | This API performs read operation on the device using opcode 0xEB                                                                               | The API assumes that the controller and the F-RAM is in SPI<br>Operating mode<br>The QUAD bit must be set prior to executing this API                                                                                                                                                                                                                                                                                                             |

| 21     | bool FRAM_DDRFastRead(uint32_t<br>address, uint8_t *read_data, uint32_t<br>read_length);                                                                                                                                                                 | This API is not tested for Revision 1.0 of this release                                                                                        | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 22     | device_mode Detect_Mode(void);                                                                                                                                                                                                                           | This API is not tested for Revision 1.0 of this release                                                                                        | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 23     | void FRAM_WRR(uint8_t *Register, uint8_t No_of_bytes);                                                                                                                                                                                                   | This API can perform writes to<br>one or all registers in the<br>device. Refer device datasheet<br>for detailed understanding of<br>the opcode | WREN command must be issued prior to executing this API. Single command be used to update Status register 1, Configuration Registers 1, 2, 4 and 5.  The Argument "No_Of_bytes" determines the number of registers that get update with this API. It is recommended to avoid using this API to ensure that unrelated register bits are not affected.  It is recommended to leverage the individual register bit manipulation APIs of this driver. |

| 23     | void FRAM_WRAR(uint32_t Reg_address, uint8_t *New_Reg_Data);                                                                                                                                                                                             | This API updates the register addressed by "Reg_address" with value pointed by "*New Reg Data"                                                 | WREN command must be issued prior to executing this API.                                                                                                                                                                                                                                                                                                                                                                                          |

| Sr. No | API Name                                                     | Description                                                                                                                                         | Notes                                                                                                                                                                                                                                        |

|--------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24     | void FRAM_RDAR(uint32_t Reg_address, uint8_t *New_Reg_Data); | This API reads the register addressed by "Reg_address" into the variable pointed by "*New_Reg_Data"                                                 |                                                                                                                                                                                                                                              |

| 25     | bool FRAM_Set_Memory_Latency(uint8_t New_latency);           | This API allows updating the memory latency values of F-RAM                                                                                         | This API is self-sufficient in terms of issues appropriate write enable commands. No other register bits are affected by this API                                                                                                            |

| 26     | bool FRAM_Set_Register_Latency(uint8_t New_latency);         | This API allows updating the register latency values of F-RAM                                                                                       | This API is self-sufficient in terms of issues appropriate write enable commands. No other register bits are affected by this API                                                                                                            |

| 27     | void FRAM_Get_Memory_Latency(void);                          | This API reads the memory latency bits from device and stores the corresponding decimal value in Mem_Latency variable of operating_mode structure   | API assumes the controller is in known operating mode (SPI,                                                                                                                                                                                  |

| 28     | void FRAM_Get_Register_Latency(void);                        | This API reads the register latency bits from device and stores the corresponding decimal value in Reg_Latency variable of operating_mode structure | DPI or QPI)                                                                                                                                                                                                                                  |

| 29     | void FRAM_QPIEN(void);                                       | Changes the operating mode of the F-RAM and controller to Quad SPI                                                                                  |                                                                                                                                                                                                                                              |

| 30     | void FRAM_DPIEN(void);                                       | Changes the operating mode of the F-RAM and controller to Dual SPI                                                                                  | This API is self-sufficient in terms of issues appropriate write enable commands. No other register bits are affected by this API                                                                                                            |

| 31     | void FRAM_SPIEN(void);                                       | Changes the operating mode of the F-RAM and controller to Standard SPI                                                                              |                                                                                                                                                                                                                                              |

| 32     | void FRAM_QUAD_ENABLE(void);                                 | Sets the QUAD bit                                                                                                                                   | QUAD bit must be set prior to executing any o the extended SPI opcodes. Refer F-RAM datasheet for details. This API is self-sufficient in terms of issues appropriate write enable commands. No other register bits are affected by this API |

| 33     | void FRAM_QUAD_DISABLE(void);                                | Resets the QUAD bit                                                                                                                                 | This API is self-sufficient in terms of issues appropriate write enable commands. No other register bits are affected by this API                                                                                                            |

# A. Appendix

#### A.1 CY15FRAMKIT-002 Kit Block Diagram

#### A.2 CY15FRAMKIT-002 Kit Components Placement

#### A.3 CY15FRAMKIT-002 Kit Schematic

### A.4 Pin Assignment Table

This section provides the pin map of the headers and their usage.

#### Arduino Compatible Headers (J1, J2, J3, J4)

|       | J1             |                       |                             |  |  |

|-------|----------------|-----------------------|-----------------------------|--|--|

| Pin   | Arduino Signal | ST Controller Signals | CY15FRAMKIT-002 Kit Signals |  |  |

| J1_1  | D8             | PB6                   | I/O3_A                      |  |  |

| J1_2  | PWM / D9       | PA8                   | WP#_I/O2_A                  |  |  |

| J1_3  | PWM/CS/D10     | PA11                  | CS#_A                       |  |  |

| J1_4  | PWM / MOSI/D11 | PB15                  | SI_I/O0_A                   |  |  |

| J1_5  | MISO / D12     | PB14                  | SO_I/O1_A                   |  |  |

| J1_6  | SCK / D13      | PB13                  | SCK_A                       |  |  |

| J1_7  | GND            | -                     | GND                         |  |  |

| J1_8  | AVDO           | -                     | NC                          |  |  |

| J1_9  | SDA / D14      | PB7                   | NC                          |  |  |

| J1_10 | SCL / D15      | PB8                   | NC                          |  |  |

|      | J2             |                       |                             |  |  |

|------|----------------|-----------------------|-----------------------------|--|--|

| Pin  | Arduino Signal | ST Controller Signals | CY15FRAMKIT-002 Kit Signals |  |  |

| J2_1 | NC             | -                     | NC                          |  |  |

| J2_2 | IOREF          | -                     | NC                          |  |  |

| J2_3 | NRST           | NRST                  | NC                          |  |  |

| J2_4 | 3V3            | -                     | 3V3                         |  |  |

| J2_5 | 5V             | -                     | 5V0                         |  |  |

| J2_6 | GND            | -                     | GND                         |  |  |

| J2_7 | GND            | -                     | GND                         |  |  |

| J2_8 | VIN            | -                     | NC                          |  |  |

|      | J3             |                       |                             |  |

|------|----------------|-----------------------|-----------------------------|--|

| Pin  | Arduino Signal | ST Controller Signals | CY15FRAMKIT-002 Kit Signals |  |

| J3_1 | RX/D0          | PA3/PA10              | NC                          |  |

| J3_2 | TX/D1          | PA2/PA9               | NC                          |  |

| J3_3 | D2             | PA12                  | CS1#_A                      |  |

| J3_4 | PWM / D3       | PB3                   | NC                          |  |

| J3_5 | D4             | PB5                   | NC                          |  |

| J3_6 | PWM/D5         | PA15                  | NC                          |  |

| J3_7 | PWM/D6         | PB10                  | NC                          |  |

| J3_8 | D7             | PC7                   | SHDN#_A                     |  |

|      | J4             |                       |                             |

|------|----------------|-----------------------|-----------------------------|

| Pin  | Arduino Signal | ST Controller Signals | CY15FRAMKIT-002 Kit Signals |

| J4_1 | A0             | PA0                   | NC                          |

| J4_2 | A1             | PA1                   | NC                          |

| J4_3 | A2             | PC3                   | NC                          |

| J4_4 | A3             | PC2                   | NC                          |

| J4_5 | A4             | PC1                   | NC                          |

| J4_6 | A5             | PC0                   | NC                          |

## Morpho Compatible Headers (J11, J12)

| Pin         ST Controller Signals         CY15FRAMKIT-002 Kit Signals           J11 1         PC9         NC           J11 2         PC8         NC           J11 3         PB8         NC           J11 4         PC6         NC           J11 5         PB7         NC           J11 6         PC5         NC           J11 7         AVDD         NC           J11 8         5V-STLINK         NC           J11 9         GND         GND           J11 10         PB0         SO VO1 M           J11 11         PB13         NC           J11 12         PA10         NC           J11 13         PB13         NC           J11 14         PA9         NC           J11 15         PB15         NC           J11 16         PB11         CS# M           J11 16         PB11         CS# M           J11 18         PB2         NC           J11 19         PA8         NC           J11 19         PA8         NC           J11 12         PB6         NC           J11 20         GND         GND           J11 21         PB6 | J11    |                       |                             |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------|-----------------------------|--|--|

| J11_2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Pin    | ST Controller Signals | CY15FRAMKIT-002 Kit Signals |  |  |

| J11_3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | J11_1  | PC9                   | NC                          |  |  |

| J11_4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | J11_2  | PC8                   |                             |  |  |

| J11_5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | J11_3  | PB8                   | NC                          |  |  |

| J11_6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | J11_4  | PC6                   | NC                          |  |  |

| J11_7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | J11_5  | PB7                   | NC                          |  |  |

| J11_8         5V-STLINK         NC           J11_9         GND         GND           J11_10         PB0         SO_VO1_M           J11_11         PB13         NC           J11_12         PA10         NC           J11_13         PB14         NC           J11_14         PA9         NC           J11_15         PB15         NC           J11_16         PB11         CS#_M           J11_17         PA11         NC           J11_18         PB2         NC           J11_19         PA8         NC           J11_19         PA8         NC           J11_21         PB6         NC           J11_22         PB1         SL_VO_M           J11_23         PC7         SHDN#_M           J11_24         PA7         WP#_VO_M           J11_25         PB10         SCK_M           J11_26         PA6         I/O3_M           J11_27         PA15         NC           J11_28         PA5         NC           J11_29         PB5         NC           J11_30         PA4         NC           J11_31         PB3         N    | J11_6  | PC5                   | NC                          |  |  |

| J11_9         GND         GND           J11_10         PB0         SO_VO1_M           J11_11         PB13         NC           J11_12         PA10         NC           J11_13         PB14         NC           J11_14         PA9         NC           J11_15         PB15         NC           J11_16         PB11         CS# M           J11_17         PA11         NC           J11_18         PB2         NC           J11_19         PA8         NC           J11_20         GND         GND           J11_21         PB6         NC           J11_22         PB1         SI_VOO_M           J11_23         PC7         SHDN#_M           J11_24         PA7         WP#_VO2_M           J11_25         PB10         SCK_M           J11_26         PA6         I/O3_M           J11_27         PA15         NC           J11_28         PA5         NC           J11_29         PB5         NC           J11_31         PB3         NC           J11_32         AGND         NC           J11_33         PA4         NC    | J11_7  | AVDD                  | NC                          |  |  |

| J11_10         PB0         SO_VO1_M           J11_11         PB13         NC           J11_12         PA10         NC           J11_13         PB14         NC           J11_14         PA9         NC           J11_15         PB15         NC           J11_16         PB11         CS#M           J11_17         PA11         NC           J11_18         PB2         NC           J11_19         PA8         NC           J11_20         GND         GND           J11_21         PB6         NC           J11_22         PB1         SI_VO0_M           J11_23         PC7         SHDN#_M           J11_24         PA7         WP#_VO2_M           J11_25         PB10         SCK_M           J11_26         PA6         I/O3_M           J11_27         PA15         NC           J11_28         PA5         NC           J11_29         PB5         NC           J11_30         PA4         NC           J11_31         PB3         NC           J11_32         AGND         NC           J11_33         PA12         CS    | J11_8  | 5V-STLINK             | NC                          |  |  |

| J11_11         PB13         NC           J11_12         PA10         NC           J11_13         PB14         NC           J11_14         PA9         NC           J11_15         PB15         NC           J11_16         PB11         CS# M           J11_17         PA11         NC           J11_18         PB2         NC           J11_19         PA8         NC           J11_19         PA8         NC           J11_20         GND         GND           J11_21         PB6         NC           J11_22         PB1         S_I/OO_M           J11_23         PC7         SHDN#_M           J11_24         PA7         WP#_I/O2_M           J11_25         PB10         SCK_M           J11_26         PA6         I/O3_M           J11_27         PA15         NC           J11_28         PA5         NC           J11_29         PB5         NC           J11_30         PA4         NC           J11_31         PB3         NC           J11_32         AGND         NC           J11_33         PA12         CS1#_M    | J11_9  | GND                   | GND                         |  |  |

| J11_12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | J11_10 | PB0                   | SO_I/O1_M                   |  |  |

| J11_13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | J11_11 | PB13                  | NC                          |  |  |

| J11_14         PA9         NC           J11_15         PB15         NC           J11_16         PB11         CS#_M           J11_17         PA11         NC           J11_18         PB2         NC           J11_19         PA8         NC           J11_20         GND         GND           J11_21         PB6         NC           J11_22         PB1         SI_I/O0_M           J11_23         PC7         SHDN#_M           J11_24         PA7         WP#_I/O2_M           J11_25         PB10         SCK_M           J11_26         PA6         I/O3_M           J11_27         PA15         NC           J11_28         PA5         NC           J11_29         PB5         NC           J11_30         PA4         NC           J11_31         PB3         NC           J11_32         AGND         NC           J11_34         PC4         NC           J11_35         PA2/PA9         NC           J11_36         PA3         NC           J11_37         PA3/PA10         NC                                          | J11_12 | PA10                  | NC                          |  |  |

| J11_15         PB15         NC           J11_16         PB11         CS#_M           J11_17         PA11         NC           J11_18         PB2         NC           J11_19         PA8         NC           J11_20         GND         GND           J11_21         PB6         NC           J11_22         PB1         SI_I/O0_M           J11_23         PC7         SHDN#_M           J11_24         PA7         WP#_I/O2_M           J11_25         PB10         SCK_M           J11_26         PA6         I/O3_M           J11_27         PA15         NC           J11_28         PA5         NC           J11_29         PB5         NC           J11_30         PA4         NC           J11_31         PB3         NC           J11_32         AGND         NC           J11_33         PA12         CS1#_M           J11_34         PC4         NC           J11_35         PA2/PA9         NC           J11_37         PA3/PA10         NC                                                                             | J11_13 | PB14                  | NC                          |  |  |