USB superspeed peripherals Forum Discussions

If, at power-on reset, the EZ-USB detects an EEPROM connected

to its I2C with the value 0xC2 at address zero.

what is that value 0xC2?where it will be?

what is referencing ''at address zero"?

Show LessHi, There

I'm using fx3 gpif II connect to fpga to get data. I've designed gpif state machine and tested using auto many to one mode and it works. I then followed the AN75779 image sensor sample and switched to manual many to one dma channel because we need to add some header information or insert some packet. However I've been stuck for a couple of days struggling to make it work. The dma callback is called but if I make any calls like CyU3PDmaMultiChannelGetBuffer or CommitBuffer/DiscarBuffer my whole program stuck, the output from my main thread also stops. It seems to me it somehow crashed. If I debug using openOCD I cannot see what are the errors.

Does anybody has any suggestions on what might cause the problem or how to debug this situation?

thanks

Joe

Show Lessi want to interface eeprom for booting and rtc,temperature sensortrough i2c with fx2lp.

i have found i2c example in this path C:\Cypress\USB\CY3684_EZ-USB_FX2LP_DVK\1.1\Target\Lib\LP

1)i2c.c

2)i2c_rw.c

when to use these .c file?

both are same?

can i use these i2c functions to interface both eeprom(boot loading)and rtc??

Show LessHow ez-usb-fx2lp automatically loads c2 load eeprom boot(24LC128-16KB-2 bytes address)?

which eeprom will select if i connect two eeprom with same size to fx2lp on I2C bus?

Show LessHello,

I have a UAC device that can output different audio sample rate 32kHz/44.1kHz/48kHz via setting, then is connected to PC via USB.

In FX3 firmware code, I have already modified some USB descriptors to support multiple sampling frequencies, as follow:

At Type I Format descriptor,

(1) increase the number of sampling frequencies (bSamFreqType)

(2) list up available frequencies

(3) Tune the size of Type I format descriptor, by the increased bytes for frequencies

(4) Tune wMaxPacketSize of the endpoint descriptor, so that it covers the samples of the greatest frequency

(5) Set the bit 0 (Sampling Frequency control) of bmAttributes on Audio-Streaming Class-specific (AS-CS) endpoint descriptor.

(6) Tune the size of wTotalLength field of the Configuration descriptor

/* Class specific AS Format descriptor - Type I Format Descriptor ???*/

0x11, /* Descriptor size */

0x24, /* Class-specific Interface Descriptor Type */

0x02, /* Format Type Descriptor subtype */

0x01, /* PCM FORMAT_TYPE_I */

0x02, /* Number of channels - 2 */

0x02, /* Subframe size - 2 bytes per audio subframe */

0x10, /* Bit resolution - 16 bits */

0x03, /* Number of samping frequencies - 1 */

0x00, 0x7D,0x00, //32kHz

0x44, 0xAC, 0x00, //44.1kHz

0x80, 0xBB, 0x00, /* Sampling frequency - 48000 Hz */

But per modifying code above, as amcap run on the pc, it doesn't have sound for all these three audio sample rate. So, I am not sure whether I need to modify or add other code. how do I tell PC which sampling frequency to use?

Thanks.

Show LessHello,

As the Technical Reference Manual suggests to use External I2S_MCLK to CX3 for high-quality audio. I have two questions to ask:

1) What do you mean by High-Quality Audio, could you please be more elaborate? I'm asking this because I'm hearing unwanted noise when given for standard audio quality testing whereas i haven't heard any noise during normal audio playback at 44.1kHz, 16 bit, Mono, Continuous Padding mode, auto DMA configuration.

2) How do i configure CX3 to take the External clock as input? I have tried using GCTL_I2S_CORE_CLK register using pointer as there is no provision for API to configure this register. But as per the note i cannot reset the CX3 as I'm having other threads and peripherals which are running, thus tried resetting only the I2S Module using I2S_POWER register. Also, a point to note was that, the I2S_Init() as well as I2S_SetConfig is modifying the register while calling I2S_SetClock(), thus i had to modify the GCTL_I2S_CORE_CLK only after the above two functions are called. It lead to modification of the MCLK but no output from BCLK or WCLK while playback from host.

Can you please suggest some instructions to use External I2S_Mclk or some good validated setup with hardware and firmware to test for good quality audio?

Earliest reply would be really grateful.

Thanks and Regards

S.Dinesh

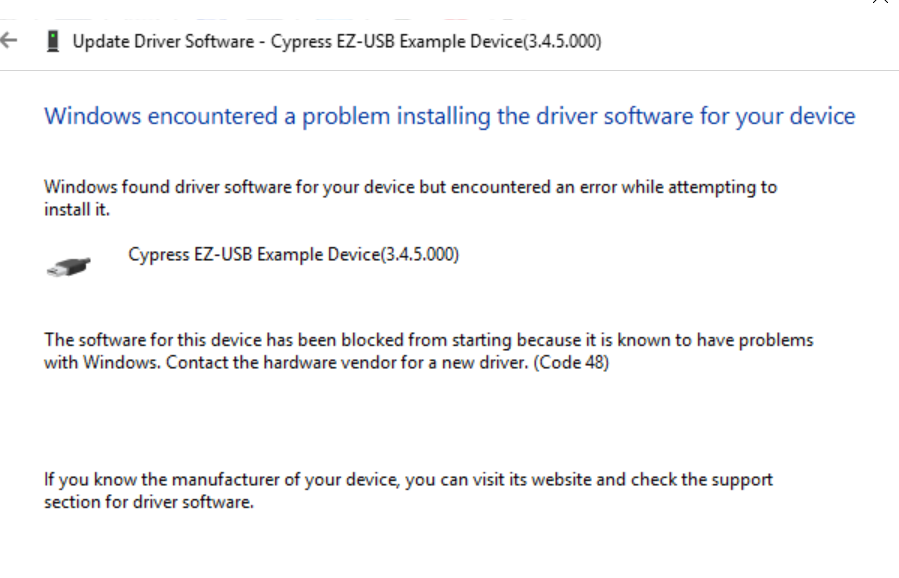

Show LessI follow Cypress CyUsb3.sys Programmer's Reference to change .inf file with no rename CYUSB3.SYS.

1. Locate the [Strings] section at the bottom of the CYUSB3.INF file.

2. Change the quoted CYUSB3_Provider string.

3. Change the quoted CYUSB3_DisplayName string.

4. Change the quoted CYUSB3_Company string.

5. Change the quoted CYUSB3_Description string.

and I re-install this changed driver. but failed.

And I want to re-install the Initial driver, but failed.

The software for this device has been blocked from starting because it is know to have problems with Windows.

Contact the hardware vendor for a new driver(code 48)

more information show as bellow.

How can I do?

I have a ZTEX FPGA board with CYUSB3033x Device combined with Xilinx 7 series FPGA which has FX3 capability.

In this example of FX2LP with ZTEX FPGA boards, it is said that we have to add CyUsb.sys for configuring firmware.

http://www.cypress.com/file/44551/download

In FX3, configuring USB devices with USb Control Center requires CyUsb.sys driver. There is an example for adding a device with 0x4B4 which is Cypress USB ID in CyUsb.pdf

However, there is no example for adding devices with different USB ID's.

I want to configure my ZTEX 2 series board with USB Control Center, to make it I need cyusb3.sys driver. Although I follow all of the steps on FX3 cyusb3.sys device adding my device cannot work in Windows 8.1.

Are there any example for adding different vendor ID device on cyusb.sys ?

or are there any trick or method adding non-cypress devices on cyus.sys?

Show LessFrom the schematic of the FX3 GPIO-to-HSMC adapter (CYUSB3ACC-006) it appears that the signals are placed somewhat randomly - some of the CTL and DQ signals go to one pin in a differential pair on the HSMC connector, and some share a pair with another signal. Is there any reason for this routing?

I'd like to create my own FX3-to-HSMC adapter PCB and re-route some of the CTL signals so I can expose 4 differential pairs on the HSMC connector and use them for another input to the FPGA board. I'd probably keep the pin-out the same except I'd move PMODE2 and CTL3 to the other side of J1C. Will changing the HSMC pins of these signals cause any issues?

Thanks!

-Colin