USB superspeed peripherals Forum Discussions

text.format{('custom.tabs.no.results')}

Customer uses CX3 as UVC USB controller and run on Android platform.

The problem is that the libuvc driver can’t parsing the frame EOF correctly due to the EOF filed in 12 bytes frame header keeps the same.

Do you have any suggestion about this ?

Or Can you share some successful Android UVC Driver and example code to us ?

Show LessHi,

Is there any way to disable SSC on FX3 ?

Hi,

I am looking for a legacy EZ USB FX3 SDK version 1.3.3 for Linux (FX3_SDK_Linux.tar.gz or whatever it was called).

The archives page https://www.cypress.com/documentation/software-and-drivers/ez-usb-fx3-sdk-archives offers only Windows downloads.

Any idea where I can find the Linux version?

Show LessHi Sir,

I have a question about config SPI

io_cfg.useSpi = CyFalse; <- use this setting , the CX3 can work well

io_cfg.useSpi = CyTrue; <- use this setting , the CX3 can not work, the E-CAM can not recognized CX3

it seems the PC host not get the CX3 descriptor.

My setting as below:

#define DUMMY_COMPLEX_GPIO 56

main()

{

...

/* Configure the IO matrix for the device.*/

io_cfg.isDQ32Bit = CyFalse;

io_cfg.useUart = CyTrue;

io_cfg.useI2C = CyTrue;

io_cfg.useI2S = CyFalse;

io_cfg.useSpi = CyFalse;

io_cfg.lppMode = CY_U3P_IO_MATRIX_LPP_DEFAULT;

/* No GPIOs are enabled. */

io_cfg.gpioSimpleEn[0] = 0;

io_cfg.gpioSimpleEn[1] = 0;

io_cfg.gpioComplexEn[0] = 0x0;

io_cfg.gpioComplexEn[1] = 0x1<<(DUMMY_COMPLEX_GPIO-32);

status = CyU3PDeviceConfigureIOMatrix (&io_cfg);

}

BR

Ben

Show LessHello,

I am considering the CYUSB302x, CYUSB303x, CYUSB202x, for my project, but I would like to know the serial write performance when these devices are in MMC-DDR52 mode. So it is a High Speed mode , with Dual Data Rate in 52MHz. I would like to use 1 pin to transfert my data so the transfert will be serial.

Could you tell me what is this serial write performance ?

Regards

Show Less- Target: I want to transfer data from host to FPGA with CYUSB3014 in super speed mode.

- Implementation:win10

- Firmware: AN65974 with slavefifo2bit, endpoint 0x01 and 0x81, bulk mode,watermark = 6, FlagC and FlagD for 0x01 to transfer data from host to fpga

- Verilog: fpga_master_streamIN_OUT_ZLP.v from AN65974, I only use the streamOUT mode

- Phenomenon : when I transfer data from host to fpga , I met the following situation.

- Case1 : when I transfer data from host to fpga at first time, the FlagD can work,but the FPGA timing is not correct, as the picture 1.1 showed. When I transfer data from host to fpga at second time, the FlagD can’t work. When I transfer data from host to fpga at third time, the FlagD can’t work and the control center tell me “error 997”,as the picture 1.2 showed.

- Case 2: after power off and restart the project, when I transfer data from host to fpga at first time, the FlagD can work,but the FPGA timing is not correct, as the picture 2.1 showed. However, the timing in picture2.1 is different from the timing in picture 1.1. When I transfer data from host to fpga at second time, the FlagD can work and I can get the correct data from fpga , as the picture 2.2 and picture 2.3 showed.

- Question:

- Can you help me to explain the different case? I never change any configurations for the project between case1 and case2.

- How can I transfer the data correctly?

AN79938 contains the recommended PAD design for NSMD. This document seems to have only information on 165-FBGA.

Is there any information on the recommended PAD design for the 121-BGA NSMD?

Thanks,

Tetsuo

Show LessThere was an application in my project.Fpga transferred an ACK frame to the host when fpga received a CMD frame from the host.The length of ACK and CMD is 32B.The GPIF II interface is a half_duplex interface, so how many CLKs should be kept at least bewteen writing and reading?I found that if set different CLKs between reading and writing,it would go wrong.FPGA could recevie CMD frame correctly;I can capture the time sequence of writing,it is right;But the ACK frame received by xferdata funtion lost the first 4B,and the last 4B is 00000000;If i transferred CMD and recevied ACK by control center,it shows that the fx3 buffer only have 31B data.Could you give me some advice?thanks a lot.

Some based settings in my design:

datawidth:32bit

fclk:100MHz

watervalue: 6

buffer size :16KB

buffer count:2

Show Less

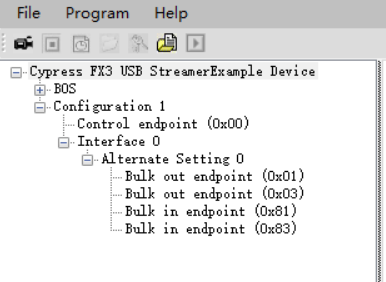

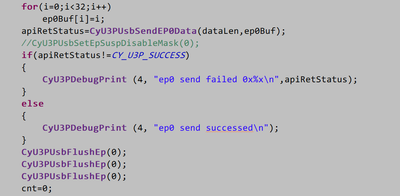

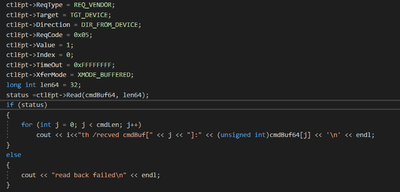

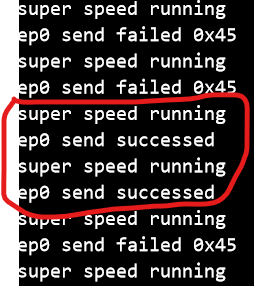

Hi,i use the fx3 to set a data link between PC and FPGA. On the USB control center,0x01 0x03 0x81 0x83 bulk endpoint serve as data transmission in auto dma mode from GPIF-II to usb(fig-1),endpoint 0 work as command transmission channel。I use function CyU3PUsbSendEP0Data(dataLen,ep0Buf) (fig-2)to send back data ,use the controlendpoint class implementation Read(PUCHAR buf, LONG &len) (fig-3)on PC ,fx3 shows that fx3 ep0 has send the data successfully, but PC get a failure as shown fig-5. Has any invalid operation?HELP me,thx!

fig-1 (USB CONTROL CENTER )

fig-2(FX3 SDK EP0 send data code)

fig-3 (PC reading ep0 data code)

fig-4 (fx3 uart print the statue of fx3 ep0 sending)

fig-5 ( print the status of PC ep0 data reading)

Show Less

Following the threads here: Re: FX3 SDK version 1.3.4 won't put breakpoints while running , is there a fix or workaround for this problem? The workaround suggested in the mentioned thread says to revert back to SDK 1.3.3. But as the OP in that thread pointed out, https://www.cypress.com/documentation/software-and-drivers/ez-usb-fx3-sdk-archives does not contain the Eclipse version and plugins that was included with SDK 1.3.3. Abhinav's reply in that thread says he attached the 1.3.3 SDK installer, but I don't see it. Can someone reupload the 1.3.3 SDK installer?

Thank you,

David

Show Less