PSoC™ 6 Forum Discussions

In the description of cyhal_i2c_master_write():

"I2C master blocking write.

This will write size bytes of data from the buffer pointed to by data. It will not return until either all of the data has been written, or the timeout has elapsed"

Will this function also block the interrupts (e.g. uart, timer ) until it finished?

Show Less

Hey Sir,

MCU CY8C6347BZI-BLD54 is used as a CPU on our product and it has been produced for 50K-100K units. However, there are a few units (less than 1%) having boot-up issue after executing the process of secure boot. The failure symptoms are listed below:

1. Power up for several cycles and then finally it could boot up successfully. The cycle time of powering up can't be calculated. It's a random.

2. Always fail to boot up so it becomes a brick.

3. 1 unit succeeds to boot up intermittently.

The eFuse of these units is burned successfully if we check the eFuse bit after the unit succeed to boot up. Thus, we can't read any debug information from the SWD port. Then some signal waveforms are captured and compared on both the situation of successful and fail boot-up. The main differences are

1. The power rail behavior of MCU_VIND2, MCU_VRF, and MCU_VBUCK1

2. The activated timing of SWDIO

Please refer to the attachment for more detail waveforms. We suspect this issue results from the process of eFuse burning but we don't have solid evidence to prove it. Thus, we need your thoughts and insights on this issue. It's getting more critical now due to the increasing production volume. Thanks.

Show LessI pre-ordered this CY8CKIT-062-BLE dev board from Digi-Key and it was shipped 28-SEP-2017 Inv # 59555866.

It won't program. I've tried the on-board Kitprog and a Miniprog. I've updated the KitProg using PSOC Programmer. I've tried updating via fw-loader. Nothing works. From within PSOC Creator 4.4, Kitprog says it programmed. The miniprog won't program from within PSOC Creator 4.4.

I looked at the silicon and it says "ES" as in "Engineering Sample" CY8C6347BZI-BLD53ES1725 62 5565. The board sticker says "121-60367-01 Rev 08" and "1732SO00102". I read online there were issues with the early versions of this board and to contact support. I sent a message via the Infineon website but I'm not sure that it went to the right place.

Is there something I can do to make this board usable? I know it's been a long time... I just recently got back into working with motor controls and I need the features present in the PSOC 6.

Show LessI don't know how to connect the VREF pin(49pin).

Should I connect a capacitor?

If so, how much capacity should I connect?

I am trying to get CE220960 working for PDL 3.1.5 to I can incorporate BLE DFU in my project which uses PDL 3.1.5. I was able to get the project to build (see my previous post ), but now I am having an issue updating the stack application (App1) using. I am using PSoC Creator 4.4, PDL 3.1.5, DFU_BLE_Upgradable_Stack_Apps, CySmart 1.3, and CY8CKIT-062-BLE hardware.

Using CySmart, I am able to do the "Application only update" which is App 2, but I there is an error when executing the Application and stack update. I get the following error:

Not sure how this could be happening because the DFU update is the same application that's already on the device, so it should just fit right in where the other instalment was. I tried increasing the size of each flash region with no luck. Any idea what could be going wrong here?

Show LessHi

The PSoC-6 PDL lists some Clock functions, but when I use them in PSoC Creator, they are not identified or declared.

these include:

Cy_SysClk_ClkPathGetFrequency() and Cy_SysClk_ClkHfGetFrequency()

I am using PDL 3.1.5

Do I have to include certain headers or libraries to the project ?

thanks

Show LessExcuse me.

There is a problem that has been bothering me for a long time.

I would like to know how to set the code optimization level in Modus Tool.

Thank you .

Show LessIn case some budys is going to use PSoC6 and FreeRTOS implement tickless idel, i would like to post my experience here.

I use creator 4.4 found CE223508_PSoC6_BLE_MultiSlave_RTOS already implemented tickless idel. Key 2 points are:

defined #define configUSE_TICKLESS_IDLE 1 //in FreeRTOSConfig.h

implmented void vApplicationSleep(TickType_t ) in tickless_idle.c

Whith these implementation. when OS get into idel task, it set MCWDT's counterMatchValue according xExpectedIdleTime.

then put PSoC in deepsleep mode. waiting MCWDT's interrupt. After exit from deepsleep, it Correct the RTOS Kernel's tick count to account for the time spent in the Deep Sleep mode

Use this CE223508, the default/maximum deepsleep time is (0xffff/32kHz) is about 2 second.

if you want a longer deepsleep time. you can modify the MCWDT. I use cascade C0C1. get a 1kHz Counter1. (this is equal to current 1ms systick in OS)

Then modify the relate code in tickless_idle.c (attachment) . As this we get a maximum deepsleep time 65 second.

Show Less

Setup: PSoC Creator 4.4, PDL 3.1.5, CY8KIT-062-BLE

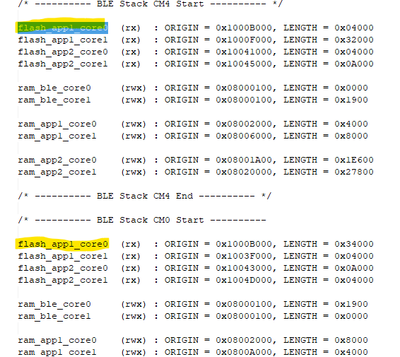

I am using PDL 3.1.5 and am trying to get CE220960 working as the first step in implementing OTA DFU in my project, but I have been having a lot of trouble with it. Right now the issue I'm stuck on is an overlapping sections error when compiling App1. Haven't seen anyone else with this issue. My process was as follows:

1. Create workspace and import DFU_BLE_Upgradable_Stack_Apps removing the parasitic "01" that PSoC Creator always tries to add to the default project names.

2. Make sure I have the correct PDL selected in Tools>Options>Project Management and in Build Settings>Peripheral Driver Library

3. Check Build Settings for all projects to make sure the correct Custom Linker Script and Post Build .bat files are referenced for CM0 and CM4 (dfu_cm0p.ld and dfu_cm4.ld).

4. Change post_build_core*.bat files to reference PDL 3.1.5 on line 11

5. Build App0 successful

6. Build App1 failed with the following error:

ERROR: section .cy_app_signature loaded at [10040ffc,10040fff] overlaps section .data loaded at [10040f90,100412e3]

collect2.exe: error: ld returned 1 exit status

The command 'arm-none-eabi-gcc.exe' failed with exit code '1'.

I'm guessing this has something to do with the flash_app*_core definitions in dfu_common.ld, but I'm having trouble figuring out how the file works. It seems like there are multiple definitions of flash_app*_core variables.

Any help is greatly appreciated!

Show Less