PSoC™ 5, 3 & 1 Forum Discussions

text.format{('custom.tabs.no.results')}

Hey All,

I have a warning that's suddenly cropping up in a design and I'm hoping I can get some input as to why exactly it is occurring and hopefully how to clear it up.

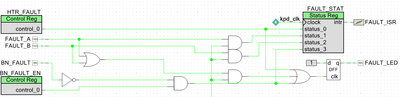

I have some custom logic to dictate the behavior of a "Fault LED" as well as a status register using a PSoC5LP (CY8C5667AXI-LP040). The internal logic schematic is below:

The idea is that I have a FAULT_STAT register to see in firmware which faults have occurred, and a LED connected to FAULT_LED that is sticky so that if any fault occurs the LED will turn ON an remain ON until a power cycle/reset occurs. Any of the faults firing will cause a rising edge on the DFF and turn FAULT_LED high.

With this setup, I receive the following on build:

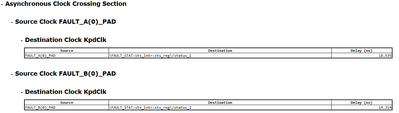

Warning-1350: Asynchronous path(s) exist from "FAULT_A(0)_PAD" to "KpdClk".

Warning-1350: Asynchronous path(s) exist from "FAULT_B(0)_PAD" to "KpdClk".

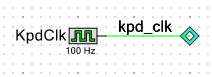

I'm not sure why this is being thrown. KpdClk is a 100Hz clock I am using mainly as a clock for the status registers that read in an external keypad. I am also using it in a few other spots such as an Edge Detector and as the source clock for a single-shot timer elsewhere in the design that should have no bearing on the issue here.

I guess I'm confused as to why this is an issue with FAULT_A and FAULT_B specifically. My first thought was maybe something about how I have these two signals controlling the CLK line of the DFF, but BN_FAULT is similarly connected as a way of controlling the DFF CLK, but the warning is not thrown for this pin. I guess I just am not seeing how FAULT_A and FAULT_B can have any relation to KpdClk, but BN_FAULT does not?

Here's a snippet info pulled from the Static Timing Analysis Document:

So what's actually going on here and how would I go about clearing up this warning? I can't share the entire project, but I can provide more details as necessary, if necessary.

Thanks!

Show LessSearching now for the n'th time for ap note project files leads me to believe

Infineon destroyed a large number of project files for PSOC.

Suggestion, go to ebay, start buying back every kit you can get your hands on,

extract DVD, and github an ISO copy of all DVDs for starters. Then ask community

for ISO copies of the ones you cant get to copy/post.

Then when biz gets good hire about 50 people to fix this sad situation.

What a tragedy......The prior Cypress website was so productive. Maybe Cypress

should have bought Infineon......

Regards, Dana.

Show LessHi,

We are using PSoC 5LP. In our workspace, there is one bootloader project and one bootloadable project, and they are link together.

We use this tool to do PSoC FW update:

Before doing PSoC FW update, we need to call Bootloadable_Load() from bootloadable project to put PSoC in bootloader mode.

We found that, after setting PSoC to bootloader mode (calling Bootloadable_Load()), PSoC stays in bootloader mode only for a couple seconds, then it goes out of bootloader mode. So if our script is quick enough, FW download to PSoC succeeds; otherwise it fails and I can tell the PSoC returns to normal application mode.

My questions are: Why bootloader mode does not stay for longer, and how to make it in bootloader state longer?

Best regards,

Winston

Show LessLooking for Ap Note project file archives ?

Regards, Dana.

Hi,

I am trying to communicate with two PSoC 5LP MCUs using the fast method so that current functions won't be affected by the latency that happens due to the communication.

So could you please suggest a method to communicate between to MCUs?

Thank you

Show LessBOARD :PSOC5LP , CY8CKIT-059, float printing is not working with USB-UART -PSOC5LP

CODE :

sprintf(charbuf,"%f\n",adc_volt) //adc_volt is float, charbuf is array

USBUART_1_PutString(charbuf);

OUTPUT : Null

Show Less

Hi,

I reviewed the datasheet associated with the AN2344 and noticed that on the Battery Pack Management System side there are no capacitors (pg. 2 of the attached datasheet). Is this accurate? The BMS appears to achieve the necessary balancing and cell protection on the battery assembly via MOSFET's and resistors. I'm hoping to receive confirmation that by using the AN2344 balanced charger that capacitors are not used in the battery assembly BMS. My application requires the presence of zero capacitors.

Any help will be greatly appreciated.

Joe DeWitt PE, PMP

Show LessAccording to the PSoC 5 datasheets:

"VDDA must be the highest voltage present on the device. All other supply pins must be less than or equal to VDDA."

What happens if, briefly this is not true? What if the VDDA supply cuts out for a moment? Can this cause actual damage to the chip?

What if it happens several times, or for a prolonged period of time? Can this cause damage to the chip?

How exact does this need to be? What if VDDA = 4.95v and VDDD = 5.00v?

Show Less

I am trying to use a variable in the "noinit" memory section. I am testing it with some very simple code:

#include "project.h"

CY_NOINIT int myVar;

int main(void)

{

CY_NOP;

myVar++;

for(;;) {}

}

I then try to use that code in the debugger. However, I see a very strange effect when I click the Reset button:

Note that I never click the Play button. I just click Reset again and again.

When I first start the debugger, I see this:

There's the code, and the CY_NOP is highlighted in yellow, meaning that line hasn't been executed yet.

Then I don't click Play.

But I just click Reset again, and this is what I see:

Look at that, myVar has increased in value by 4! Each time I click Reset, the value increases by 4. This is strange for two reasons:

- No code should have been executed yet, as I haven't clicked Play.

- There's nowhere in the code that adds 4 to the variable.

What is going on here?

Here's some more evidence:

- If I step through the code and execute the line myVar++; then I see the variable increase by 1.

- If I change the type of myVar to char, it still increases by 4.

Show Less

I've attached two really good docs that somewhat answer my question but not completely. The third .png doc shows an INL20 of +-32. Surely this must be a typo? What is the INL of the PSoC 5 when the 20 bit AtoD is used?

Same question for the enob on the PSoC 5? What is it? I realize it depends on a lot of things as the app note explains but most data sheets contain the enob info. It specced DNL and INL, power supply rejection ratio, and other parameters but no mention of enob.

Thanks.

Show Less