PSoC™ 5, 3 & 1 Forum Discussions

Looking into the generated code for the EEPROM component, I see this:

cystatus EEPROM_1_Write(const uint8 * rowData, uint8 rowNumber)

{

cystatus status;

CySpcStart();

if(rowNumber < (uint8) CY_EEPROM_NUMBER_ROWS)

{

/* See if we can get SPC. */

if(CySpcLock() == CYRET_SUCCESS)

{

/* Plan for failure */

status = CYRET_UNKNOWN;

/* Command to load a row of data */

if(CySpcLoadRow(CY_SPC_FIRST_EE_ARRAYID, rowData, CYDEV_EEPROM_ROW_SIZE) == CYRET_STARTED)

{

while(CY_SPC_BUSY)

{

/* Wait until SPC becomes idle */

}

In this code is a while() statement that relies on CY_SPC_BUSY becoming false in order for it to exit the loop.

Is there any way this code could get stuck here? Are there any circumstances (temperature, voltage fluctuations) under which CY_SPC_BUSY can stay true forever?

If EEPROM_UpdateTemperature() wasn't called recently, could this loop get stuck?

If I wanted to deliberately cause this loop to get stuck by messing with the external conditions of the chip, is there some way I could do it?

If I wanted to deliberately cause this loop to get stuck by incorrectly using the EEPROM component API, is there some way I could do it?

Show Less

We are using PSoC Creator 4.4 and have automated our builds.

In the PSoC Creator User guide, I saw the option to generate project datasheets.

Would it be possible to create these using a command line tool, such that we can integrate it in our automated build?

We would like this to work for all the four projects we have in our workspace. One project is the active project and triggers the build of the other three projects. In the user guide it mentions that the generation is done for the active project. I hope this can be specified when using a command line tool.

Show LessDoes Infineon support any implementations of Micro ROS on PSOC (4 or 5)?

If not has anyone tried this and had success?

The officially supported hardware is given here: GitHub - micro-ROS/micro_ros_setup: Support macros for building micro-ROS-based firmware.

Show LessDevice: CY8C5888LTI-LPO97

Simply trying to get print statement read out in putty. Device is connected to computer via USB connection.

Firmware has been updated.

Already checked port and pin is correct one for this hardware.

Code has not been changed. I have tired all baud rates.

Anyone I can trouble shoot this. I have no errors in the logs and nothing to tell me there is something wrong with the program. Is it possible the hardware is bad? I would appreciate any suggestions to trouble shoot.

Show Less

Hi,

I'm trying to aggressively use a hibernate mode and a WDT is intended to pull the CPU out of hibernation.

However, I need to preserve some data through the WDT reset.

Is there a keyword declaration to place certain RAM variables in an area of memory that does not get initialized immediately after a reset?

I'm aware of the .bss section of RAM. However after multiple searches among the compiler .h files, I could not find a declarative keyword that would force RAM variables to this area of memory.

I suspect I'm missing something obvious. Help would be appreciated.

Show LessHi all,

I'm having problems waking from Sleep using the SleepTimer with the PSoC5LP. I am trying to implement an auto-wake feature and would like to use the SleepTimer to wake the device when it has been asleep for 4096ms (max SleepTimer counter).

I implemented the SleepTimer_Interrupt_Sleep demo project on my development board and observed the LED indicating the toggling of the LED at the appropriate period based on the SleepTimer duration. Great. The I proved the component works...

The problem that I encountered is that the counter does not appear to be reset when SleepTimer_Stop() and SleepTimer_Start() are called. In the demo project the SleepTimer component is started prior to the main loop and never disabled. In my application, I want to enable the SleepTimer() component only when I am about to sleep. I don't want the ISR continuously executing while I the application is running. I just want to wake ~4s after going to sleep.

SleepTimer_Start();

CyPmSaveClocks();

CyPmSleep(PM_SLEEP_TIME_NONE, PM_SLEEP_SRC_CTW);

CyPmRestoreClocks();

SleepTimer_Stop();

(My SleepTimer ISR is identical to that of the demo in that it only calls SleepTimer_GetStatus() according to the driver requirements.)

The behavior I observe is when I put the device to sleep the wake period is erratic. It can be anywhere between immediately waking and the ~4s maximum period.

As a test, I moved the SleepTimer_Start() to the initialization section of my application so that it runs constantly as the demo project illustrates. I did this to prove that the SleepTimer ISR is, in fact, being called every 4096ms in my application. I then induced sleep at various times between ISRs and correctly saw the device waking at each ISR execution.

The problem appears to be when I use the SleepTimer_Start() function it is not starting the timer from 0, it is continuing the counter from where SleepTimer_Stop() was called. I have tried issuing SleepTimer_Init(), SleepTimer_SetInterval(SleepTimer__CTW_4096_MS), etc to re-initialize the SleepTimer component, but have not had any success.

How do I start the counter from 0 every time I call SleepTimer_Start()?

Thanks,

Nate

Looking for CY8C5666AXI-LP004 anyone have some they aren't using?

Hello,

did I get it right, that the PSoC 5LP devices are ranked as Legacy products?

And why they are listed under 8/16bit Legacy Microcontrollers?

What does that mean for your customers regarding support, availability,...?

BR,

Andreas

Show LessHey All,

I have a warning that's suddenly cropping up in a design and I'm hoping I can get some input as to why exactly it is occurring and hopefully how to clear it up.

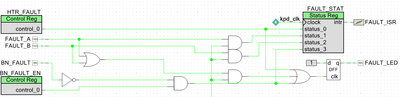

I have some custom logic to dictate the behavior of a "Fault LED" as well as a status register using a PSoC5LP (CY8C5667AXI-LP040). The internal logic schematic is below:

The idea is that I have a FAULT_STAT register to see in firmware which faults have occurred, and a LED connected to FAULT_LED that is sticky so that if any fault occurs the LED will turn ON an remain ON until a power cycle/reset occurs. Any of the faults firing will cause a rising edge on the DFF and turn FAULT_LED high.

With this setup, I receive the following on build:

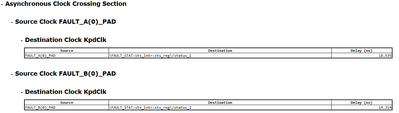

Warning-1350: Asynchronous path(s) exist from "FAULT_A(0)_PAD" to "KpdClk".

Warning-1350: Asynchronous path(s) exist from "FAULT_B(0)_PAD" to "KpdClk".

I'm not sure why this is being thrown. KpdClk is a 100Hz clock I am using mainly as a clock for the status registers that read in an external keypad. I am also using it in a few other spots such as an Edge Detector and as the source clock for a single-shot timer elsewhere in the design that should have no bearing on the issue here.

I guess I'm confused as to why this is an issue with FAULT_A and FAULT_B specifically. My first thought was maybe something about how I have these two signals controlling the CLK line of the DFF, but BN_FAULT is similarly connected as a way of controlling the DFF CLK, but the warning is not thrown for this pin. I guess I just am not seeing how FAULT_A and FAULT_B can have any relation to KpdClk, but BN_FAULT does not?

Here's a snippet info pulled from the Static Timing Analysis Document:

So what's actually going on here and how would I go about clearing up this warning? I can't share the entire project, but I can provide more details as necessary, if necessary.

Thanks!

Show LessSearching now for the n'th time for ap note project files leads me to believe

Infineon destroyed a large number of project files for PSOC.

Suggestion, go to ebay, start buying back every kit you can get your hands on,

extract DVD, and github an ISO copy of all DVDs for starters. Then ask community

for ISO copies of the ones you cant get to copy/post.

Then when biz gets good hire about 50 people to fix this sad situation.

What a tragedy......The prior Cypress website was so productive. Maybe Cypress

should have bought Infineon......

Regards, Dana.

Show Less