PSoC™ 4 Forum Discussions

I am using a CYBLE-022001 and need to verify the integrity of FLASH at startup, preferably by using a CRC calculation. I noticed in the Intel Hex File, there is a location at the end of the file that stores some sort of checksum as shown below.

:0200000490303A

:02000000E0C559

This same checksum is used and verified by PSOC programmer when the "Verify" button is clicked after programming the part. In the example above, E05C is the checksum that is verified. So my questions are:

1) Is this checksum stored in some non-volatile memory (0x90300000) location on chip and

2) If it is, where can I find the calculation that creates and/or verifies this checksum

Thank you in advance!!!

Show LessI am working on a project that has a hard requirement to perform a CRC calculation to be executed at power-on to guarantee that the internal MCU FLASH is not corrupted. After painstaking searches and personal posts on this forum, I have to the following conclusion

1) The Intel Hex must be parsed post build (with a tool built by me) and the CRC must be calculated and appended/modified to the Intel hex file at the end of the user FLASH space.

2) There is a checksum (2 bytes) at location 0x90300000 that also must be updated based on the result of the CRC calculation in order for PSOC programmer to recognize the Intel Hex file as being valid

3) Also, there is a field at location 0x90500000 (considered metadata) that also must be updated in order for the file to be considered valid by PSOC Programmer. It seems the final 2 bytes are also an additive checksum, but documentation states for Internal Use only

So my question is, are there any post build tools or methods that allows one to add a unique CRC to the end of User Flash and successfully updates both checksums (at 0x90300000 & 0x90500000) so that PSOC Programmer recognizes the Intel Hex file as valid. THANK YOU IN ADVANCE!!!

Show LessHi,community

Is there anything I should keep in mind when designing a write port (SWD) on a board using PSoC4 chips?

When I write a program to the evaluation board using mini Prog4, if the board itself is powered off, I control VTARG from the Psoc programmer to supply power.

Therefore, I recognize that the VTARG pin can be powered.

What is the behavior if the board is already powered on, as in the case of other manufacturers' debuggers?

Is there a so-called "detect function" ?

Please also let me know if there are any manuals that I should refer to when designing the hardware for the SDW terminal.

Best Regards,

Chihiro Tatebayashi

Show Less分享:J-Link Download PSoC4 & iHex2Bin & RTT printf

链接:https://xarm.gitee.io/2023/01/22/PSoC4/JLinkDLP4/

J-Link Download PSoC4 & RTT

一直遗憾于PSoC Creator不支持J-Link,摸索了一种方法可以曲线使用J-Link下载PSoC4,虽不是完美,但也还算优雅~

-

首先实现Creator生成的Hex文件转BIN。

由于Creator生成的Hex文件中包含了Meta data的内容,地址位于0x90300000~0x90600000,所以没办法直接对hex文件下载,也没办法直接使用现有的hex2bin工具实现转换。meta data的具体内容格式参考上上一篇笔记:

PSoC4 Programming & Hex file Dump:

https://xarm.gitee.io/2022/10/21/PSoC4/PSoCHexDump/可实现方法可以有:

- 手动删除hex文件后十行,去掉metadata。

- 批处理删除或写个小程序删除。

- 写个小程序,删除meta data并转存为BIN文件。

刚好前几天在 Community看见有人问如何将hex转为bin,于是就顺手写了个这个小工具,使用方式极其简单: ihex2bin.exe + *.hex即可,会自动生成同名的bin文件。可以使用J-Flash对比原hex文件及生成的bin文件的正确性。

-

移植Segger的RTT实现printf

这个就太简单了,将Segger安装目录下的RTT文件copy至工程中,然后选择 SEGGER_RTT_Syscalls_GCC.c 这个文件即可。要使用printf记得将Heap改大!RTT:Real Time Transfer,有了RTT,从此UART的printf是路人~

RTT的官网介绍:https://www.segger.com/products/debug-probes/j-link/technology/about-real-time-transfer/题外话:RTT还支持离线使用,比如你的设备运行1天后会莫名其妙的HardFault,肿么办?总不能一直挂着仿真器或串口吧?挂着仿真器即使能看到进入hardfault也没办法定位是从哪跳进hardfault来的!使用RTT+CMBackTrace可以完美的解决这个问题:等进入Hardfault后,挂上仿真器,RTTView一下,就可以了,因为信息都记录在ram中! 以后再记录这个问题。

-

Creator工程将hex文件copy至指定目录

工程选项 / Build Settings / ARM GCC5.4… / User Command / post build中写入: .\copyHex.bat

然后在工程目录文件下创建copyHex.bat,内容为:

batcopy .\CortexM0p\ARM_GCC_541\Debug\P4RTT.hex ..\JlinkDLPSoC4\P4RTT.hex

这样每次编译完成后会自动将生成的hex文件copy至JlinkDLPSoC4目录下,名称为同名称的P4RTT.hex。

-

JlinkDLPSoC4目录下放置J-Link烧录的批处理文件:

创建 S2Convert&Load.bat文件,首先将hex文件另存为bin文件,然后实现JLink的下载

batihex2bin.exe P4RTT.hex @echo off set "_DEVICE_=CY8C4147XXX-SXXX" if exist "JLink.exe" ( JLink.exe -device %_DEVICE_% -CommanderScript S2LoadJLinkFW.jlink goto END ) else ( echo JLink.exe not present in folder. Press any key in order to use windows registry to locate JLink.exe ) pause :END pause goto :EOF :ERR echo Error: J-Link software and documentation package not installed or not found. pauseS2LoadJLinkFW.jlink内容为:

batspeed 4000 si SWD r sleep 10 loadbin P4RTT.bin, 0 r g q -

剩下的就是打开RTTView,编译完成后双击S2Convert&Load.bat即可,会自动下载并运行app。如下图示:

JLink DL P4 -

欢迎留言交流,稍后更新源码下载地址。

Hi All,

In our Design we have few Capsense signals which is going to two Capsense button. Whether the Button sharing for Same signal is acceptable in PSOC-4100s Max.

Can you please provide the clarification on the same ASAP. Attached the picture for your reference.

Show Less

Hello all,

Currently i am developing software for USB-HID Touchpad.

I tested USB-HID code on CY8CKIT-041-40XX which is working fine for I2C communication.

I am using CY8C4247 AZI-L445 for my finalized project. I want to make HID touchpad using CSX(mutual capacitance) method, because of multi finger touch we need mutual capacitance.

L445 IC is not having Gesture feature, because of that i need to take touch sense without using Gesture feature.

I saw the CSX method for trackpad but in almost examples Gesture is already added.

so, I want to make touchpad development based on getting touch sense data without gesture on trackpad using CSX method. After that this all over data sends to the host using USB protocol.

Please suggest, reference document and and Program code to implement and proceed further.

Thank you for response,

Sanket More ,

India

Show LessI would like to know how to recognize the chips or boards that support IDAC7 and IDAC8. The one I used is not available, but there are several more that are hard to recognize.

I always used the CY8CKIT-059 but now is out of stock. What else can I use. Does the CY8CKIT-146 contain IDAC's? or the CY8CKIT-149? The release notes and manuals don't seem to explain. Only the CY8C58LP family datasheet mentions it, but it doesn't say which references belong to this family.

Thanks!

Show LessDear all,

I use PSoC Creator 4.2 and the project that I inherited have a CapSense component released at V7.0 and developed by PSoC Creator 4.2 too but I do not know its settings.

My PSoC Creator SW alert me about the CapSense Component: "Cannot find v 7.0 of component CapSense_P4". I tried to update the component by the option "Update Components" but I can able only to "downgrade" the component to V5.0.

I have found this discussion https://community.infineon.com/t5/PSoC-Creator-Designer/Is-PSoC-v4-2-is-not-compatible-with-CapSense-v7-0/td-p/281511 but this procedure does not work: after the downgrading of CapSense component to V5.0 and the restarting the PSoC Creator SW, the highest available version of CapSense is V5.0 still.

How can I get CapSense V7.0 with PSoC Creator 4.2?

Thanks in advance.

Show LessThis device must output, using IDAC, a biharmonic signal with two different central frequencies (100 and 200 Hz), the frequency of the second harmonic is equal to the frequency of the central frequencies / 3.

At first there should be a clean oscillation (sine wave), then after pressing the button a parasitic harmonic oscillation appears and lasts for 2 seconds, then the signal returns to the initial value.

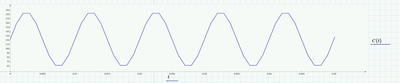

Before and after:

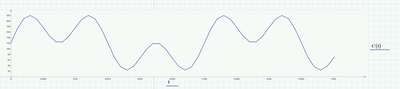

during:

During the test, I used a different frequency ratio of parasitic to normal oscillation for the second mode (not 3, but 2). Only to monitor the correctness of the mode change.

Based on the fact that the frequency changes (100 or 200 Hz), it is necessary to change the period of the output of the signal counts using interruptions (Period Timer).

It is also obvious that the call period will vary from the sampling frequency (the number of counts per period).

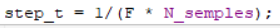

As a result, the formula for calculating the call step looks like this:

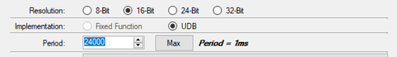

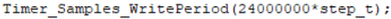

As can be seen from the above attached figure, the period is set to 24000 (1ms). The device works according to its described functionality (changing the waveform according to the mode) but with one problem, I could not change the timer period (Timer_Samples).

I tried to find something similar, but using the solutions given there, I could not get it to work. I also want to emphasize that it not only did not change, but in general stopped outputting anything when changing the mode (for the first time, everything worked, but probably most likely using the uncalculated value of "Step" in Timer_WritePeriod() and what was entered into the timer, namely 24000 (1ms ).

I will be grateful for your help, I am also attaching an archive with the project.

P.S. I did that, but the period still doesn't seem to change:

Show Less

Dear Sirs and Madams,

We are looking at configuring CapSense using PSoC4S.

I'm thinking of using a guard sensor so that it doesn't react to water. Do you have any sample code with ModusToolbox?

We have never used the guard sensor, but would like to know the best way to disable only a specific electrode when the guard sensor responds.

Unlike PSoC Creator, I think that ModusToolbox has less explanation of APIs that are suitable for CapSense.

Is it documented anywhere other than the CAT2 Peripheral Driver Library?

Regards,

Show Less