PSoC™ 4 Forum Discussions

Hello,

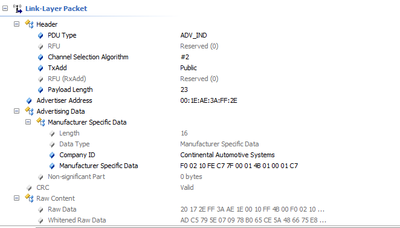

I'm using CY5677 USB dongle together CySmart 1.3. During scanning, my specific sensor which is doing advertising is not listed in Scanning window anymore even the advertising frames are visible on Android phone( e.g nrfConnect) and also visible on sniffer( I'm using an ellisys sniffer).

I have to mention other devices are listed in scanning window. Also, I have colleagues which are using this USB dongle and see the advertising frames for the same sensors.

Can you help me please to find out the root cause?

Please find bellow some details. If needed I can share with you the sniffer log.

Thank you in advance,

Regards,

Nicu

Show Less

Hi,

As per ARM documentation, Cortex-M0 LDR/STR instructions should take 2 cycles for execution. This is usually honored by the PsoC 4 MCUs, but, while accessing GPIO pins, they take 6 cycles. I am not able to find any document describing it.

Could you please help me on this?

Show Lesshttps://github.com/hackingchips/PSoC_FatFs

for PSoC4M

I am testing the microSD card program from the link above. Unfortunately, I cannot connect to the SD card.

I see the error: error : (FR_NOT_READY) sdcard not ready.

What I am doing wrong?

Show LessEven is already the latest pSocCreatorSeTUP_4.4_b80. Draw a SAR ADC to schematic. My SAR ADC version is still V2.5.. How to upgrade to SAR ADC V2.6 ?

Show LessHello,

When using an external VREF for the SARADC of CY8C4246AZI-L445, what is the maximum current required for the reference?

To be more specific, we are thinking of using LT6656AIDC-4.096 as the external reference IC.

The output current of this IC is 1uA.

Will the SARADC work properly with this IC?

Regards,

Shimamura

Hello,

We can find "Table 21-2. Negative Input Selection Comparison" in "PSoC 4100S and PSoC 4100S Plus: PSoC 4 Architecture TRM, Document No. 002-10621 Rev. *K ".

note:)I dare to change it to the representation of the data sheet of the analog coprocessor PSoC4A.

I have two questions.

1) Is there any material that expresses the Good and Best of the Maximum SNR with specific numerical values?

It doesn't seem to be on the datasheet.

2)Should the Maximum SNR be set to Best in Single-ended mode as shown in the figure below?

Best regards,

Yocchi

Show LessHi,

When a central gets to connect my peripheral device, I want to read this central's public address.

The goal is to introduce this central address in the peripheral's whitelist with the intention of allowing connection when set policy filter in mode "whitelist conn".

Any idea how to obtain central's address once connected ?

Thanks in advance,

Asier.

Show LessHi

I try assgin different value to " CapSense_dsRam.wdgtList.number1.fingerTh" to adjust button sensitivity.

When I tested it no difference.

If I need dynamically adjust capsense button sensitivity.

How can I do ?

Show LessI have used PSoC4 (4013 and 4014) for three projects recently and I have found several issues that have cost me a lot of time to work through. For example, and this is probably not everything, just off the top of my head:

if there is too much C on the VDD rail you cannot use power cycle to program. I built the little circuit that uses XRES through a buffer to drive VCC and that helps, but still too much C is still a problem.

If P1.6 is actively driven during first programming, it will not program.

Programmer will sometimes program the part while Creator will not.

My question today is - where are all of these issues documented? There are a lot of messages from users like me frustrated with these quirks. Surely they are all documented somewhere? I have searched for "errata" and I get nothing. How can that be?

Thanks -

Dan

Show LessDue to unavailability of 212019 we must migrate an existing design to 214015, which is available. We found no way to use the SCB in SPI-Mode because SCBx_CLK can only be output to P0.7 which is used for debugging. Is it correct that the 214015 has a dedicated SPI_Master which is not mentioned in the datasheet but the outputs can be routed to any GPIO ( or is it a UDB used for that )?

Also for using CapSense, in 212019 we had to add a capacitor to Cmod (P4.0) which is not present in the 214015 but the Port 4.0 appears in the Pin-List (33 of 32) of the creator. Is it an internal Pin of the module, which is in turn connected to this 2n2-capacitor?

Would be nice to have this clear before making new PCB's

Thanks

Show Less