#### AN209699

## **OTP Lock Command for SLC NAND Flash Memory**

Author: Xiaoling Lao, Mohamed Sardi

**Associated Project: No**

Associated Part Families: S34ML-1 (excluding S34ML01G1), S34ML-2,

S34MS-1 (excluding S34MS01G1), S34MS-2, S34SL-2

AN209699 documents the command set sequence that is used to permanently protect the OTP area from program operations.

#### 1 Introduction

Cypress SLC NAND products include a One Time Programmable (OTP) area, which is an additional block outside the main flash memory array where sensitive data or code can be stored permanently. A dedicated command set is used to access and permanently protect the OTP area from program operations. The OTP protection status can be read in a bit of the Status Register.

#### 2 OTP Area Protection

#### 2.1 OTP Lock Command Sequence

Table 1. OTP Area Protection Command Sequence

| Command              | 1st Cycle | 2nd Cycle | 3rd Cycle | 4th Cycle | 5th Cycle | 6th Cycle | 7th Cycle |

|----------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| OTP Entry            | 29h       | 17h       | 04h       | 19h       | -         | -         | -         |

| OTP Protection Setup | 4Ch       | 03h       | 1Dh       | 41h       | -         | -         | -         |

| Page Program         | 80h       | 00h       | 00h       | 00h       | 00h       | 00h       | 10h       |

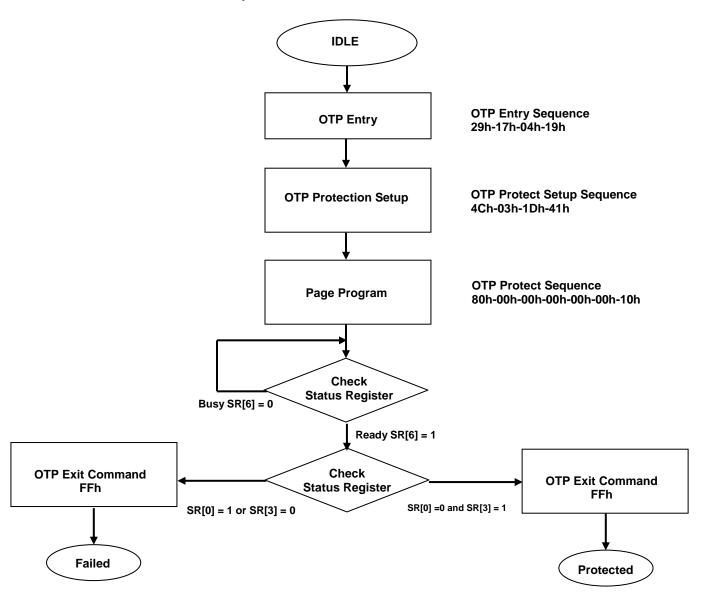

Following the OTP protection setup sequence, a page program sequence with an address of zero and without data input is issued by the host system to program the protection control bit for the OTP area. The status register read command is then used to poll the status register to determine when the programming operation is completed and verify that the OTP area is protected. To exit OTP area access mode, a Reset command (FFh) is issued by the host system.

## 2.2 Status Register

After the OTP area protect command sequence is issued by the host system, the host system can read the Status Register bit 0 (SR[0]) to check whether the operation has been completed successfully (SR[0]=0) or not (SR[0]=1). The user can read the Status Register bit 3 (SR[3]) to check whether the OPT area is protected (SR[3]=1) or not (SR[3]=0).

Table 2. Status Register Coding

| SR bit | Program/Erase     | CODING                          |  |

|--------|-------------------|---------------------------------|--|

| 0      | Pass / Fail       | Pass: '0' Fail: '1'             |  |

| 3      | Protection Status | Unprotected: '0' Protected: '1' |  |

| 6      | Ready / Busy      | Busy: '0' Ready: '1'            |  |

### 2.3 OTP Lock Command Sequence Flow Chart

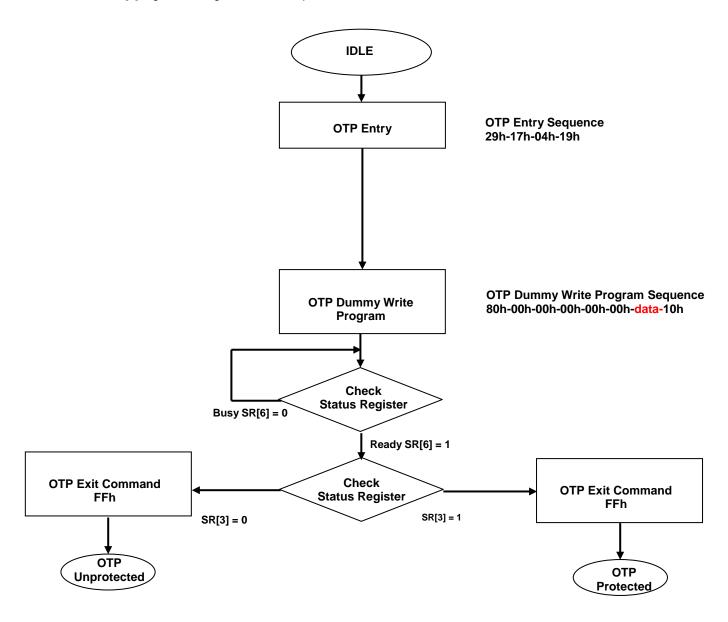

#### 2.4 OTP Read Status Sequence Flow Chart

At any given time, the host controller may want to check the OTP lock status. The sequence below highlights the different steps necessary. A dummy program operation (data=FFh or no data) must be performed prior to reading the status SR[3] register setting. Indeed such operation is used to determine whether the OTP is locked.

### 3 Related Datasheets

- 1Gb 8Gb 3.0V (ML-1) High Reliability, SLC NAND Flash Memory http://www.cypress.com/products/1gb-8gb-30v-ml-1-high-reliability-slc-nand-flash-memory

- 1Gb 16Gb 3.0V (ML-2) High Reliability, SLC NAND Flash Memory

http://www.cypress.com/products/1gb-16gb-30v-ml-2-high-reliability-slc-nand-flash-memory

- 1Gb 4Gb 1.8V (MS-1) High Reliability, SLC NAND Flash Memory

http://www.cypress.com/products/1gb-4gb-18v-ms-1-high-reliability-slc-nand-flash-memory

- 1Gb 16 Gb 1.8V (MS-2) High Reliability, SLC NAND Flash Memory

http://www.cypress.com/products/1gb-16-gb-18v-ms-2-high-reliability-slc-nand-flash-memory

- 1Gb 4Gb 3.0V (SL) High Security, SLC NAND Flash Memory http://www.cypress.com/products/1gb-4gb-30v-sl-high-security-slc-nand-flash-memory

- e.MMC Managed NAND Flash Memory

http://www.cypress.com/products/emmc-managed-nand-flash-memory

# **Document History**

Document Title: AN209699 - OTP Lock Command for SLC NAND Flash Memory

Document Number: 002-09699

| Revision | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                 |

|----------|---------|--------------------|--------------------|-----------------------------------------------------------------------|

| **       | 5046620 | XILA               | 12/21/2015         | New Spec.                                                             |

| *A       | 5216255 | МОН                | 04/14/2016         | 2.4: Added Section describing how to read the OTP status at any time. |

## **Worldwide Sales and Design Support**

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### **Products**

ARM® Cortex® Microcontrollers cypress.com/arm

Automotive cypress.com/automotive

Clocks & Buffers cypress.com/clocks

Interface cypress.com/interface

Lighting & Power Control cypress.com/powerpsoc

Memory cypress.com/memory

PSoC cypress.com/psoc

Touch Sensing cypress.com/touch

USB Controllers cypress.com/usb

Wireless/RF cypress.com/wireless

# PSoC® Solutions

cypress.com/psoc

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

## **Cypress Developer Community**

Community | Forums | Blogs | Video | Training

## **Technical Support**

cypress.com/support

PSoC is a registered trademark and PSoC Creator is a trademark of Cypress Semiconductor Corp. All other trademarks or registered trademarks referenced herein are the property of their respective owners.

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-

Phone Fax Website : 408-943-2600 : 408-943-4730 : www.cypress.com

© Cypress Semiconductor Corporation, 2015-2016. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you under its copyright rights in the Software, a personal, non-exclusive, nontransferable license (without the right to sublicense) (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units. Cypress also grants you a personal, non-exclusive, nontransferable, license (without the right to sublicense) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely to the minimum extent that is necessary for you to exercise your rights under the copyright license granted in the previous sentence. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and Company shall and hereby does release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. Company shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.