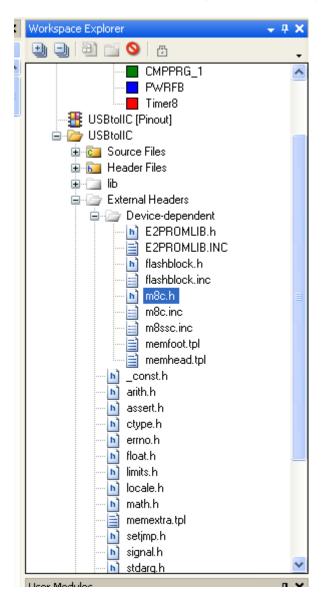

## Location of m8c.h - Source Files/External Headers/Device-dependent

## Definition of the registers and bits of PSoC 1 in m8c.h

```

Start Page USBtoIIC [Chip] main.c m8c.h

298

//-----

300 // Analog Control Registers

301

302

303

AMX IN:

0x060 // Analog Input Multiplexor Control

#pragma ioport

304

AMX IN;

(0x0C)

305

#define AMX IN ACI1

306

#define AMX IN ACIO

(0x03)

307

308 #pragma ioport AMUXCFG: 0x061 // Analog MUX Configuration

309 BYTE

AMUXCFG;

310 #define AMUXCFG BCOL1MUX (0x80)

311 #define AMUXCFG ACOLOMUX (0x40)

312 #define AMUXCFG INTCAP (0x30)

313 #define AMUXCFG MUXCLK (0x0E)

314 #define AMUXCFG EN

(0x01)

315

316 #pragma ioport ARF_CR:

0x063 // Analog Reference Control Register

317 BYTE

ARF_CR;

#define ARF_CR_HBE (0x40)

318

319

#define ARF_CR_REF

(0x38)

#define ARF_CR_REFPWR

320

(0x07)

321

#define ARF CR SCPWR

(0x03)

322

323 #pragma ioport

CMP CRO:

0x064 // Analog Comparator Bus Register O

CMP CRO;

324 BYTE

325 #define CMP CRO COMP1 (0x20)

326 #define CMP CRO COMPO (0x10)

327 #define CMP CRO AINT1 (0x02)

328 #define CMP_CRO_AINTO (0x01)

329

#pragma ioport

0x065 // Analog Synchronizaton Control Register

330

ASY CR:

ASY CR;

331

BYTE

332

#define ASY CR SARCOUNT (0x70)

333

#define ASY_CR_SARSIGN (0x08)

334

#define ASY_CR_SARCOL (0x06)

335 #define ASY CR SYNCEN (0x01)

336

0x066 // Analog Comparator Bus Register 1

337 #pragma ioport CMP CR1:

338 BYTE CMP CR1;

220 #dofine CMD CD1 CINTG1

```