### **AN2099**

# PSoC<sup>®</sup> 1, PSoC 3, PSoC 4, and PSoC 5LP - Single-Pole Infinite Impulse Response (IIR) Filters

Author: David Van Ess, Praveen Sekar

**Associated Project: Yes**

Associated Part Family: All PSoC<sup>®</sup> 1, PSoC 3 and PSoC 5LP parts Software Version: PSoC Creator™, PSoC Designer™

**Related Application Notes: None**

AN2099 describes a topology for a single-pole infinite impulse response (IIR) filter. It includes equations and software to implement this topology; the associated example projects give the user access to filter routines in either assembly or C.

### Introduction

In the real world analog signals are noisy; one example might be the output voltage of a thermistor. It is often undesirable to display or use this noisy data. The best way to remove or "clean up" the noise is to apply a filter to the signal. Ideally, the filter removes the noise and keeps the signal of interest. Filters exist in the analog domain that can be used to reduce noise. However, this results in extra cost and power consumption of an analog filter. That is where digital filters come in. IIR filters can be used to approximate many common analog filters.

This application note derives the transfer function of a first order IIR Low Pass and High Pass Filter. Based on these transfer functions, the C and ASM code for a Low Pass Filter are derived. Three example projects are provided with this application note to provide hands-on examples of how the filters work.

# Infinite Impulse Response (IIR) Filters

An IIR filter is a recursive filter; that is, the output is used to calculate future values. Theoretically, an impulse injected into the input continues to flow through the signal loop. It takes infinite time for the effect of the impulse to die down completely.

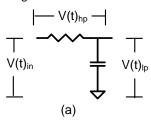

The single-pole passive RC filter shown in Figure 1 has the characteristics of an IIR filter. If you give an impulse input, it takes an infinite time for the capacitor voltage to go completely to zero.

We will build the topology of the single-pole IIR digital filter from the single-pole passive RC filter shown in Figure 1.

Figure 1. Single-Pole Passive RC Filters

In Figure 1, the low-pass filter output is available across the capacitor and the high-pass filter output is available across the resistor.

The output voltage,  $V_{lp}$ , at any instant is a function of the current flowing into the capacitor which is a function of  $V_{in}$ - $V_{ln}$ . This represents a negative feedback.

To construct a negative feedback equivalent to the analog RC filter in Figure 1, consider the following statements:

- At any instant, V<sub>in</sub>-V<sub>ip</sub> is divided by R to give a current, which is then integrated to give V<sub>ip</sub>.

- V<sub>in</sub>-V<sub>lp</sub> represents the high-pass filtered output.

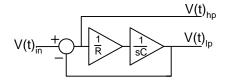

Figure 2 shows the negative feedback topology equivalent to that in Figure 1.

Figure 2. Negative Feedback Topology for Single-Pole RC Filter

1

Equations 1 and 2 define its operation:

$$V_{hp} = V_{in} - V_{lp}$$

Equation 1

$$V_{lp} = \frac{V_{hp}}{sCR}$$

Equation 2

Combining Equations 1 and 2 produces the transfer functions in Equations 3 and 4:

$$\frac{V_{hp}}{V_{in}} = \frac{sCR}{1 + sCR}$$

Equation 3

$$\frac{V_{lp}}{V_{in}} = \frac{1}{1 + sCR}$$

Equation 4

These are the standard transfer functions for high-pass and low-pass filters. The roll-off frequency  $f_0$  is shown in Equation 5:

$$f_0 = \frac{1}{2\pi CR}$$

Equation 5

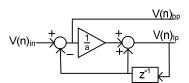

The topology for a sampled system is constructed from the topology in Figure 2 and is shown in Figure 3.

Figure 3 shows that the integrator is replaced with an accumulator (summer), and the term CR is replaced by a scaling factor. The  $z^{-1}$  box represents a register that stores the previous value of  $V(n)_{lo}$ .

Figure 3. IIR Topology for Sampled Single-Pole RC Filters

Equations 6 and 7 define its operation:

$$V_{hp} = V_{in} - V_{lp} z^{-1}$$

Equation 6

$$V_{lp} = \frac{V_{hp}}{a} + V_{lp} z^{-1}$$

Equation 7

where z<sup>-1</sup> represents a unit sample delay. Replacing z<sup>-1</sup> with a unit sample delay gives the difference (see Equations 8 and 9).

$$V_{hn}(n) = V_{in} - V_{ln}(n-1)$$

Equation 8

$$V_{lp}(n) = \frac{V_{hp}(n)}{a} + V_{lp}(n-1)$$

Equation 9

Combining Equations 6 and 7, we get the transfer functions in Equations 10 and 11.

$$\frac{V_{hp}}{V_{in}} = \frac{a(1-z^{-1})}{a+z^{-1}(1-a)}$$

Equation 10

$$\frac{V_{lp}}{V_{in}} = \frac{1}{a + z^{-1}(1 - a)}$$

**Equation 11**

It can be shown that the roll-off frequency  $f_0$  for the digital filter represented by Equations 6 and 7 can be approximated by Equation 12. (See Appendix A)

$$f_0 = \frac{f_s}{2\pi a}$$

Equation 12

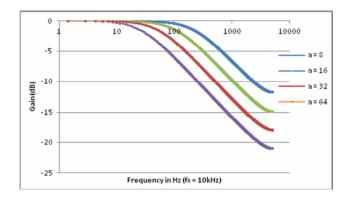

Equation 12 is the same as Equation 5 with RC = a. The roll-off frequency is dependent on the sample frequency  $f_s$ , but more importantly the attenuation value (a). Changing the attenuation value easily changes the filter's roll-off frequency. If you increase the attenuation factor, you can lower the filter cut-off frequency. However, this results in an increased filter settling time.

Figure 4. Filter Cut-off Versus Attenuation Factor

## **Filter Settling Time**

Settling time in a low-pass filter is the time taken by the output to reach a certain percentage of a step input.

For the analog RC low-pass filter shown in Figure 1, the output for a step input will be an exponential rise defined by Equation 11.

$$V_{out} = V_{in}(1 - e^{-t/RC})$$

Equation 13

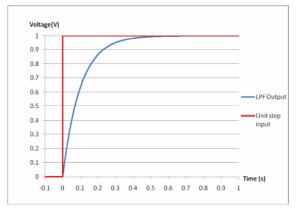

For  $V_{in}=1\ V,\ R=1\ k,$  and  $C=10\ uF,$  the filter settling ( $V_{out}\ Vs$  time) for a unit step input is shown by the blue line in Figure 5.

Figure 5. Analog LPF Unit Step Response

To find the time taken by the filter to reach 99.9% of the input, we substitute,  $V_{out}=0.999;\ V_{in}=1;\ R=1\ k;\ C=10\ uF$  in Equation 13.

$$0.999 = (1 - e^{-100t})$$

or

t = 0.7 s

0.7 seconds are necessary to reach 99.9% of the step input. This time depends on the choice of R and C.

Similar to the analog low-pass filter output, the digital low-pass filter output also takes a finite time to reach within a certain percentage of its input. In this case, the settling time is determined by the attenuation factor, **a**.

It can be shown (see Appendix B) that for a unit step input, the amplitude of the nth sample output, s[n], is given by Equation 14.

$$s[n] = 1 - \left(1 - \frac{1}{a}\right)^n$$

Equation 14

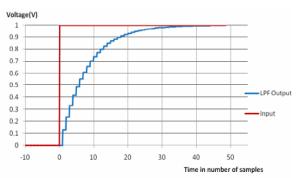

Equation 14 is the digital equivalent of Equation 13 with  $V_{in} = 1$ . Figure 6 plots s[n] (the unit step response) Vs n (the number of samples) for an attenuation factor of 8. The red line shows the input and the blue line shows the filter output.

Figure 6. Digital LPF Unit Step Response

To calculate the number (n) of samples required for the output to reach 99.9% of the input, you must substitute s[n] = 0.999 in Equation 14 and compute n.

$$0.999 = 1 - \left(1 - \frac{1}{8}\right)^n \quad \text{or} \quad$$

$$n = \sim 52$$

It takes 52 samples for the filter to reach 99.9% of the input voltage. If you filter an ADC output using this LPF (a=8) and if the ADC sample rate is 52 sps, it takes approximately a second for the filter to reach 99.9% of the ADC input voltage.

The filter settling time is also specified in terms of number of bits.

The settling time for the filter output to reach n-bit accuracy is the time taken by the filter to settle to within

$$(1-\frac{1}{2^n})$$

\* input voltage.

Table 1 shows the settling time for 10, 12, and 16-bit accuracies.

For 10-bit accuracy, the output should reach within 0.1% of the input value; For 12-bit accuracy, the output should reach within 0.025% of the input value, and for 16-bit accuracy, the output should reach within 0.0015% of the input value. For a 1-V input, the filter achieves 10-bit accuracy at 999.03 mV, 12-bit accuracy at 999.75 mV, and 16-bit accuracy at 999.985 mV.

Table 1. Filter Settling Times

| Attenuation Factor, a | 10-bit<br>Accuracy | 12-bit<br>Accuracy | 16-bit<br>Accuracy |

|-----------------------|--------------------|--------------------|--------------------|

| 1                     | 0                  | 0                  | 0                  |

| 2                     | 10                 | 12                 | 16                 |

| 4                     | 25                 | 29                 | 39                 |

| 8                     | 52                 | 63                 | 84                 |

| 16                    | 108                | 129                | 173                |

| 32                    | 219                | 262                | 350                |

| 64                    | 441                | 527                | 706                |

| 128                   | 885                | 1058               | 1417               |

| 256                   | 1765               | 2120               | 2838               |

## How to Implement an IIR LPF

To implement the low-pass and high-pass filters shown in Figure 3, we can directly use Equations 8 and 9. The steps are as follows:

- Using your sample frequency (f<sub>s</sub>) and the roll-off frequency that you want to use (f<sub>0</sub>), find the necessary divisor (a) using Equation 12.

- 2. Subtract the old  $V_{lp}$  from  $V_{in}$ . This is the new  $V_{hp}$ .

- 3. Divide V<sub>hp</sub> by a.

- Add the value generated in step 3 to the old V<sub>Ip</sub>. This

is the new V<sub>Ip</sub>. Note that only V<sub>Ip</sub> needs to be saved

for the calculation of the next values.

Step 3 requires you to perform a division (involves floating point arithmetic) by the attenuation factor (a), which can take any real value greater than unity. If you choose the attenuation factor carefully, you can perform the division with just shifts and add. Let us limit the attenuation factor to this set of values:

$$a = \left\{ \frac{256}{255}, \frac{256}{254}, \frac{256}{253}, \dots, \frac{256}{1} \right\}$$

Equation 15

For example, if the attenuation factor is 256/99, Equation 9 becomes:

$$V_{lp}(n) = V_{lp}(n-1) + (V_{in}(n) - V_{lp}(n-1)) * \frac{99}{256}$$

Equation 16

$$\frac{99}{256} = \frac{64}{256} + \frac{32}{256} + \frac{2}{256} + \frac{1}{256} = \frac{1}{4} + \frac{1}{8} + \frac{1}{128} + \frac{1}{256}$$

This can be easily done by a combination of shifts and adds, as shown by the C code snippet (Code 1). The variable 'filt' denotes the low-pass filter output and the variable 'input' denotes the low-pass filter input.

#### Code 1

Similarly, any attenuation factor in the set can be implemented with just shifts and additions.

The negative side of limiting the attenuation factor in this way is that you may not have enough choices when the attenuation factor gets higher. For example, if you want an attenuation factor of 145, you must use 128 or 256. But if you want an attenuation factor of 6.5, you can choose a value very close to it, 6.5 which is 256/39. But, this should not be a serious problem because higher attenuation factors are generally not desired due to their higher settling times.

For most practical purposes, you might require an attenuation factor in the range of 4 to 64 and can easily match it to one of the available values.

## **Binary Weighted IIR Filters**

If the value of the attenuation factor, a, is a power of 2, it is much easier to implement the filter. All that is required is one shift and one addition. If the attenuation factor is 2<sup>^1</sup>, the filtering can be done very easily using the following line of code.

This executes much faster and takes less code space as well. In most cases, digital filtering is done to reduce the noise, where the requirement to implement the actual cut-off frequency is not stringent. Binary-weighted IIR filters can be used in those cases.

## Single-pole IIR Filter versus Moving Average FIR Filter

A moving average filter is also commonly used for reducing noise in the digital output. A moving average filter is implemented by simply taking the average of the last N samples as defined by Equation 17. The higher the value of N, the lower is the filter cut-off.

$$y[n] = \frac{x[n] + x[n-1] + x[n-2] + \dots + x[N-1]}{N}$$

Equation 17

The pros and cons of the moving average filter and the single-pole IIR filter are as follows.

- A single-pole IIR filter is easy to implement and requires a storage space of just one memory element to store the past output. However, the settling time increases as the attenuation factor increases and the filter takes infinite samples to settle to the input value.

- A moving average FIR filter is relatively complex to implement and requires a storage space of N elements, where N is the number of samples averaged. The filter takes just N samples to settle to the input value.

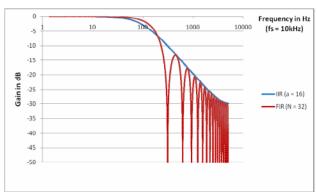

- A moving average filter with N elements has a frequency response roll-off comparable to an IIR filter with attenuation factor, a = N/2. Or, in other words, the roll-off of a 32-tap moving average filter can be matched by an IIR filter with an attenuation factor of just 16. Figure 7 shows the frequency response performance of a 32-element moving average filter and a single-pole IIR filter of attenuation factor, 16.

However, if you compare time responses, you can see that it takes 108 samples (Table 1) for the IIR filter to settle to 99.9% of the input while the moving average FIR takes just 32 samples to settle to 100% of the input signal.

|                               | Single-pole IIR       | Moving Average FIR            |  |

|-------------------------------|-----------------------|-------------------------------|--|

| Defining parameter            | Attenuation factor, a | Number of samples averaged, N |  |

| Firmware implementation       | Easy                  | Relatively complex            |  |

| Memory<br>storage<br>required | Single-pole IIR       | Moving Average FIR            |  |

| Settling time                 | Infinite              | N                             |  |

Figure 7. Frequency Responses of Moving Average and Single-Pole IIR filters

## **Associated Projects**

This application note includes four projects:

- IIR\_Filter\_PSoC3\_5 PSoC Creator workspace containing two projects, one for PSoC 3 (IIR\_PSoC3) and one for PSoC5 (IIR\_PSoC5)

- AN2099\_asm PSoC designer project for PSoC 1 in assembly

- AN2099\_C -PSoC designer project for PSoC 1 in C.

# **PSoC 3 Filter Implementation**

The PSoC Creator project, IIR\_PSoC3, performs low-pass filtering on the 20-bit delta sigma ADC output and displays the filtered and unfiltered value on the LCD.

The filter routine takes the filter input as an argument and returns the filtered output after low-pass filtering the input data with an attenuation factor of 16.

#### Code 2

```

int32 LowPassFilter(int32 input)

{

int32 k;

input <<= 8;</pre>

```

```

filt = filt + ((input-filt) >> 4);

k = (filt>>8) + ((filt & 0x00000080) >> 7);

return k;

```

In this code, the statement

```

filt = filt + ((input-filt) >> 4);

```

performs the filtering with an attenuation factor of 16. The attenuation factor can be easily changed to the required value by replacing this line of code with a code similar to Code 1 (code 1 implements an attenuation factor of 2.56)

The variable 'input' is the input to the low-pass filter. The variable 'filt' is a long int variable that accumulates the filter running sum.

To avoid any loss of precision due to right shifts, we left shift the input variable. The input is left-shifted by 8 so that we can perform a right shift of 8 (maximum right shift for a = 256) without losing precision. For this reason, the variable filter should at least be 8 bits wider than the input. The variable 'filter' is declared a long int variable while the 'input' is declared an int variable. This left-shift by 8 is compensated by performing a right-shift by 8 before returning the LPF output. This is done by the following statement.

```

k = (filt >> 8) + ((filt & 0x00000080) >> 7);

```

While right-shifting, perform rounding-off instead of truncation. The additive term ((filt &  $0 \times 00000080$ ) >> 7) checks the Most Significant bit (bit 8) of the bits shifted out and performs the round-off before shifting the 8 bits out.

# PSoC 4 and PSoC 5LP Filter Implementation

In PSoC 4 and PSoC 5LP, the filtering can be done much faster due to the availability of a single-cycle multiply instruction in ARM cortex M0 and M3. In PSoC 4 and PSoC 5LP, the filter routine for a low-pass filter (a = 256/17) looks like this:

#### Code 3

```

int32 LowPassFilter(int32 input)

{

int32 k;

input <<= 8;

filt = filt + (((input-filt) >> 8) * 17);

k = (filt>>8) + ((filt & 0x00000080) >> 7);

return k;

}

```

The third statement performs the filtering. As you can see, the division by 256 is done by right-shifting by 8 and the multiplication is performed directly (without shift and add). It is very easy to change the attenuation factor to any value in Equation 15 by directly changing the value 17 to

the required value. Note that the division is performed before the multiplication so that the variable filt stays within the int32 limit.

If you program the PSoC Creator project in a PSoC 5LP chip, you can see that the filtered value is comparatively more stable than the raw ADC output. Try changing the attenuation factor (a), and notice the change in settling time and stability of the filtered output.

The PSoC 4 project is designed to work on the CY8CKIT-042. This kit does not have an LCD. Thus the data is output via UART on P4.1 (Pin 9 of J10). Connect this pin to Pin 9 of J11 (the 12-pin header next to the USB connector).

Plug a USB cable between your computer and the CY8CKIT-042. Next, open the Cypress Bridge Control Panel. In the **Connected I2C/SPI/RX8 Ports:** dialog, you should see a COM port that corresponds to the CY8CKIT-042 (for example COM8). Click on this COM port.

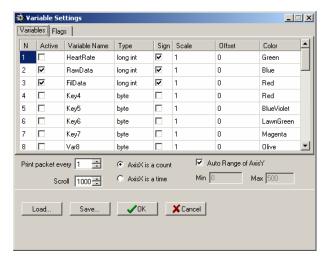

Next, click the Tools menu option and select Protocol Configuration. Configure it to match Figure 8.

Figure 8: RX8 Protocol Configuration

After you have configured the protocol, go to the Chart Menu and select Variable Settings. Configure it to match Figure 9.

Figure 9: Variable settings for COM Port

Now go to back to the editor and type the following command:

rx8 [h=aa] @2RawData @1RawData @0RawData @2FilData @1FilData @0FilData [t=55]

Hit the Repeat button and then move to the Chart tab. You should now be able to see a graph of the data. You can move the input voltage around to see how the filtered and raw data change.

### Filter Feedforward

Filter feedforward eliminates the filter for a fast changing input. If the input changes from 0 V to 5 V, the filter takes 108 iterations (attenuation factor = 16) to reach 4.995 V. This delay can be reduced by including a feedforward term to Code 3. Code 4 modifies Code 3 to include the feedforward term.

#### Code 4

In Code 4, the 'if else' structure ensures that the filter is not applied when the input value exceeds the current filter value by more than 100. The feedforward term is multiplied by 256 to bring it in the same order as the input (the input is multiplied by 256 inside the filter code). If there is a sudden change in input, say, from 0 V to 5 V (0 counts to 2^19 counts), the filter will not be applied and the filtered value will reach the input value instantaneously. The input will be filtered only when the input change is < 100 counts. To ensure that noise is filtered, the feedforward coefficient should be higher than the peak-to-peak noise.

## **PSoC 1 Filter Implementation**

The two PSoC 1 based projects provide both low-pass and high-pass filter functions written in assembly. The functions have been written in assembly in PSoC 1 because the PSoC 1 CPU is low MIPS compared to that of PSoC 3 and PSoC 5LP. The functions can be found in the file *IIRFilters.asm* in the PSoC Designer project. One project has the main file written in assembly and the other project has the main file in C.

Both projects are similar to the PSoC Creator project in that they take the ADC input and show both the ADC output and low-pass filtered output in an LCD.

## IIR High-Pass Filter - PSoC 1

The iSimpleHighPassFilter function in the file IIRFilters.asm implements a high-pass filter with an attenuation factor of 256. Equation 18 defines the roll-off frequency. An attenuation of 256 is selected because it can easily be implemented with a byte shift.

$$f_0 = \frac{f_s}{2\pi 256} = \frac{f_s}{1608}$$

Equation 18

For a sample rate of 5 ksps, the roll-off frequency is 3.1 Hz.

The function takes a 16-bit signed input and, using the old  $V_{lp}$ , calculates the next value. The new 16-bit  $V_{hp}$  is returned. This function assumes that 16-bit data is input through the X (MSByte) and A (LSByte) registers. The output is a 16-bit high-pass value returned through the X and A registers. Code 5 shows the function.

This function is not called in the project. Only the iSimpleLowPassFilter function is called. But if needed, you can call this function in your project the same way the iSimpleLowPassFilter function is called.

#### Code 4

```

area bss(RAM)

BLK 3

iVlp:

;[iVlp]

= MSByte

;[iVlp + 1] = LSByte

;[iVlp + 2] = Residue

area text(ROM,REL)

export SimpleHighPassFilter

export _SimpleHighPassFilter

;; SimpleHighPassFilter:

;;

Take input and output new

;;

;; highpassvalue

;; INPUTS: X,A Vin

OUTPUTS: X,A Vhp

;;-----

SimpleHighPassFilter:

```

```

_SimpleHighPassFilter:

sub A,[iVlp+1]

swap A,X

sbb A,[iVlp]

; Vhp now in A, X

cmp A,128 ;test if Vhp is neg

swap A,X

if1: jc elseif1 ;(if neg)

add [iVlp+2],A

swap X,A

adc [iVlp+1],A

swap A,X

adc [iVlp],ffh ;extended neg sign

ret

elseif1:;(pos)

add [iVlp+2],A

swap X,A

adc [iVlp+1],A

swap A,X

adc [iVlp],0 ;extended pos sign

ret.

endif1:

```

An initialization function is required to set the initial value for  $V_{lp}$ . Code 6 shows this function:

#### Code 5

```

;; SimpleHighPassInit:

;;

;; Initializes the Vlp value

;; INPUTS: X,A Init Value

;; OUTPUTS: None.

;;

SimpleHighPassInit:

_SimpleHighPassInit:

_mov [iVlp],X

_mov [iVlp + 1],A

_mov [iVlp + 2],0

ret

;;

```

#### IIR Low Pass Filter - PSoC 1

The iSimpleLowPassFilter function implements a low-pass filter with attenuation factor 256/12. The cut-off frequency is given by Equation 19. To change the attenuation, you have to change the SHIFT ACCUM sequence in the assembly code.

$$f_0 = \frac{f_s * 12}{2\pi 256} = \frac{f_s}{134}$$

Equation 19

Code 7 is the function that takes a 16-bit signed input and, using the old  $V_{lp}$ , calculates the next value. The new 16-bit  $V_{lp}$  is returned:

#### Code 6

```

macro SHIFT

asr [TempReg]

rrc [TempReg + 1]

rrc [TempReg + 2]

endm

```

```

macro ACCUM

mov A, [TempReg + 2]

add [iVlp1 + 2],A

mov A, [TempReg + 1]

adc [iVlp1 + 1],A

mov A,[TempReg]

adc [iVlp1],A

endm

export iSimpleLowPassFilter

export _iSimpleLowPassFilter

;;-----

;; iSimpleLowPassFilter:

;;

;; Take input and output new

;; higpassvalue

INPUTS: X,A Vin

;; OUTPUTS: X,A Vhp

iSimpleLowPassFilter:

_iSimpleLowPassFilter:

push A

mov A,0

sub A,[iVlp1+2]

mov [TempReg + 2],A

pop A

sbb A,[iVlp1+1]

mov [TempReg + 1],A

mov A,X

sbb A,[iVlp1]

mov [TempReg],A

SHIFT

SHIFT

SHIFT

SHIFT

SHIFT

ACCUM ;32

SHIFT

ACCUM ;64

mov A,[iVlp1 + 2]

add A,128

mov X,[iVlp1]

mov A,[iVlp1 + 1]

adc A,0

swap X,A

adc A,0

swap X,A

```

This function also requires an initialization function. It is shown in Code 7:

### Code 7

```

export SimpleLowPassInit

export _SimpleLowPassInit

;;------

;; SimpleLowPassInit:

;;

;; Initializes the Vlp value

;; INPUTS: X,A Init Value

;; OUTPUTS: None.

```

## **Summary**

Single-pole IIR filters are useful for removing noise from useful signals. Four projects have been presented that can easily be tailored to your filtering requirements.

## Appendix A

The actual cut-off frequency for the single-pole low-pass filter can be derived from Equation 20

$$\frac{V_{lp}}{V_{ln}} = \frac{1}{a + z^{-1}(1 - a)}$$

Equation 20

Substituting  $z^{-1} = e^{-jw}$ , we get,

$$\frac{V_{lp}}{V_{in}} = \frac{1}{a + e^{-jw}(1 - a)}$$

$$\frac{V_{lp}}{V_{in}} = \frac{1}{a + (\cos w - j\sin w)(1 - a)}$$

The magnitude of the transfer function is given by Equation 21

$$\left| \frac{V_{lp}}{V_{in}} \right| = \frac{1}{\sqrt{\left( (a + (1 - a)\cos w)^2 + ((1 - a)\sin w)^2 \right)}}$$

Equation 21

$$\left| \frac{V_{lp}}{V_{in}} \right| = \frac{1}{\sqrt{\left( (1 + 2a^2 - 2a(1 - (1 - a)\cos w) + a^2 + a^2) + a^2 +$$

At the cut-off frequency (w = w<sub>0</sub>),  $\left| \frac{V_{lp}}{V_{in}} \right| = \frac{1}{\sqrt{2}}$

$$\frac{1}{\sqrt{2}} = \frac{1}{\sqrt{\left((1+2a^2-2a(1-(1-a)\cos w_0)\right)}}$$

or

$$f_0 = \frac{f_s}{2\pi}\cos^{-1}\left(1-\frac{1}{2a(a-1)}\right)$$

Equation 22

Equation 21 gives the actual expression for the cut-off frequency for the single-pole low-pass IIR filter. However, for a >8 (filter attenuation factors commonly used are between 8 and 64), Equation 21 can be approximated by Equation 23:

$$f_0 = \frac{f_s}{2\pi a}$$

Equation 23

Table 3 shows the difference between the two cut-off frequencies (Equations 12 and 21) at different values of attenuation factor at a sample frequency of 10 kHz.

Table 3. Cut-off Frequency Approximation Error

| а   | Cut-off Calculated using Equation 12 | Actual Cut-off<br>(Equation 21) |  |

|-----|--------------------------------------|---------------------------------|--|

| 2   | 795.7747155                          | 1150.267281                     |  |

| 4   | 397.8873577                          | 461.0511704                     |  |

| 8   | 198.9436789                          | 212.8383013                     |  |

| 16  | 99.47183943                          | 102.7519182                     |  |

| 32  | 49.73591972                          | 50.53386767                     |  |

| 64  | 24.86795986                          | 25.0648066                      |  |

| 128 | 12.43397993                          | 12.48286862                     |  |

| 256 | 6.216989965                          | 6.229172189                     |  |

## **Appendix B**

The settling time of the single-pole digital IIR filter can be derived from Equation 11, which is re-written below

$$\frac{V_{lp}}{V_{in}} = \frac{1}{a - z^{-1}(a - 1)}$$

Equation 24

If you rearrange Equation 24, you get Equation 25, which is the frequency response of a digital low-pass filter with attenuation factor, a.

$$H(z) = \left(\frac{1}{a}\right) \frac{1}{1 - z^{-1}\left(1 - \frac{1}{a}\right)}$$

Equation 25

If you take inverse z-transform, you get the impulse response of the filter (h[n]).

$$h[n] = \left(\frac{1}{a}\right) \left(1 - \frac{1}{a}\right)^n$$

Equation 26

Summation of the impulse response over 0 to n samples gives the unit step response (s[n]).

$$s[n] = \left(\frac{1}{a}\right) \sum_{0}^{n} \left(1 - \frac{1}{a}\right)^{n}$$

Equation 27

Simplifying Equation 27, we get Equation 28

$$s[n] = 1 - \left(1 - \frac{1}{a}\right)^n$$

Equation 28

# **Document History**

Document Title: PSoC® 1, PSoC 3, PSoC 4, and PSoC 5LP - Single-Pole Infinite Impulse Response (IIR) Filters – AN2099

Document Number: 001-38007

| Revision | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                           |

|----------|---------|--------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------|

| **       | 1520284 | DWV                | 10/01/2007         | Old application note updated to CY web.                                                                                         |

| *A       | 2711571 | YARA               | 05/27/2009         | Added CY8C29x66, CY8C27x43, CY8C24x23A, CY8C24x94, CY8C21xxx, and CY8C20xxx part families.  Updated Software version to PD 5.0. |

| *B       | 3248285 | DSG                | 05/04/2011         | Added section Implementation in C                                                                                               |

| *C       | 3394927 | PFZ                | 10/12/2011         | Major rewrite of the document                                                                                                   |

| *D       | 3457966 | PFZ                | 12/09/2011         | Template Update Updated project for PSoC Creator 2.0                                                                            |

| *E       | 3492061 | PFZ                | 01/11/2012         | Fixed Table 2.                                                                                                                  |

| *F       | 3806325 | RRSH               | 11/27/2012         | Updated for PSoC 5LP.                                                                                                           |

| *G       | 4202704 | TDU                | 11/26/2013         | Added PSoC 4 Project. Fixed Equation 14. Corrected equation reference in Appendix B.                                            |

| *H       | 4373327 | TDU                | 05/08/2014         | No Change                                                                                                                       |

## **Worldwide Sales and Design Support**

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

## **Products**

Automotive cypress.com/go/automotive cypress.com/go/clocks

Interface cypress.com/go/interface

Lighting & Power Control cypress.com/go/powerpsoc cypress.com/go/plc

Memory cypress.com/go/memory

PSoC cypress.com/go/psoc

Touch Sensing cypress.com/go/touch

USB Controllers cypress.com/go/usb

Wireless/RF cypress.com/go/wireless

## PSoC® Solutions

psoc.cypress.com/solutions PSoC 1 | PSoC 3 | PSoC 5LP

## **Cypress Developer Community**

Community | Forums | Blogs | Video | Training

## **Technical Support**

cypress.com/go/support

All other trademarks or registered trademarks referenced herein are the property of their respective owners.

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709 Phone Fax Website : 408-943-2600 : 408-943-4730 : www.cypress.com

© Cypress Semiconductor Corporation, 2007-2014. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

This Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges. Use may be limited by and subject to the applicable Cypress software license agreement.