# SIO Tips and Tricks in PSoC® 3 / PSoC 5

# AN60580

Author: Pavankumar Vibhute

Associated Project: Yes

Associated Part Family: CY8C38xxxx

Software Version: PSoC® Creator™

Associated Application Notes: None

# **Application Note Abstract**

The special input/output (SIO) pins provide differential input buffer and a means to regulate the high level output voltage ( $V_{OH}$ ). The SIO pins are tolerant to input voltages higher than the I/O supply voltage and can sink up to 25 mA current. This application note explains the following applications of SIO pins: Comparator, Charge pump, Salen-key filter, Level shifter, Half wave rectifier, Peak detector, and Sleep wakeup using SIO Comparator.

#### Introduction

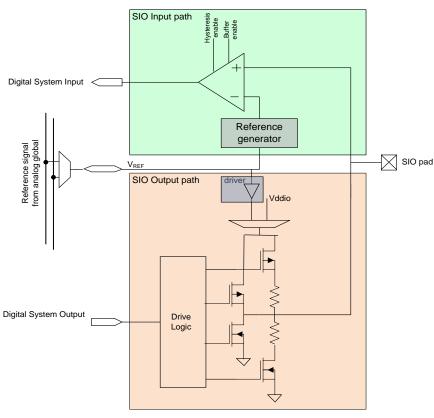

The SIO input can be set as a single ended or a differential input. When configured as a single ended input, the SIO acts similar to a normal GPIO with standard CMOS and LVTTL input levels. However, when configured as a differential input it acts as a comparator. The reference generator block provides the threshold for the comparator.

The SIO output level can be set as a standard CMOS output or a regulated output. In regulated output mode, the  $V_{REF}$  signal selected from Analog Global sets the  $V_{OH}$  level. The SIO architecture is shown in Figure 1.

PSoC<sup>®</sup> 3 and PSoC 5 devices have eight SIO pins that are organized as four pin pairs. A pair of SIO pins shares a common reference generator block. Refer to the Technical Reference Manual (TRM) for more details.

Figure 1. SIO Architecture

# SIO Configuration in PSoC Creator™

#### SIO Input Configuration

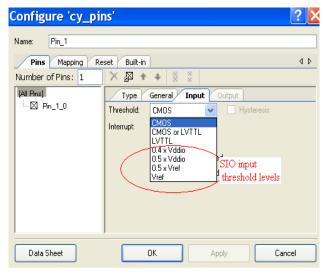

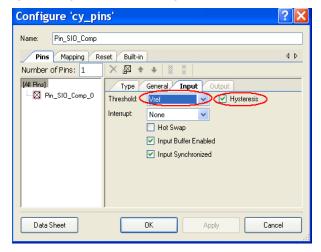

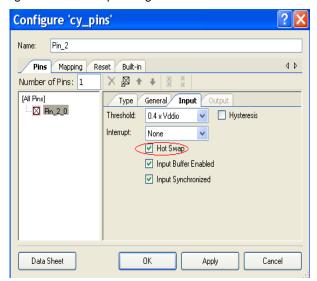

The Digital Input Pin component configuration screen is shown in Figure 2. Selecting one of the four threshold options circled in red configures the pin as SIO in differential input mode.

Figure 2. Digital Input Pin Configuration

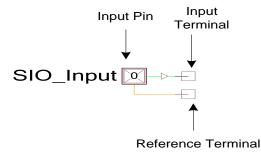

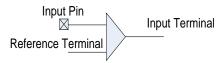

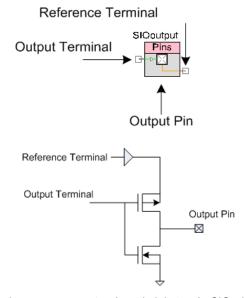

Selecting 0.5 x  $V_{REF}$  and  $V_{REF}$  threshold options add Reference Terminal to the Digital Input Pin component. This allows to route external reference from other components such as DAC or Pin.

Figure 3. Routing External Reference for Differential Input

This component uses SIO pin if Hot Swap is enabled and threshold is set to anything other than LVTTL or CMOS. **Note** The outline in pink indicates that the Digital Input Pin component uses SIO pin.

#### SIO Output Configuration

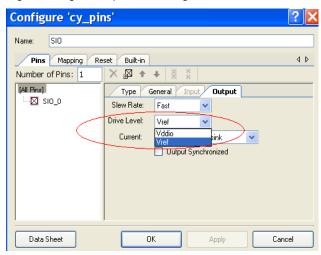

The Digital Output Pin component configuration screen is shown in Figure 4.

Figure 4. Digital Output Pin Configuration

Select  $V_{\text{REF}}$  Drive Level option to configure the pin as SIO in regulated output mode. It adds reference terminal to the Digital Output Pin component. This allows to route external reference from other components such as DAC or Pin

Figure 5. Routing External Reference for Regulated Output

GPIO pins can source 4 mA and sink 8 mA; SIO pins can source 4 mA and sink 25 mA.

This component uses SIO pin if Drive Level is set to  $\ensuremath{V_{REF}},$  and Drive Current is set to a 25 mA sink.

**Note** The outline in pink indicates that the Digital Output Pin component uses SIO pin.

#### **Tip 1: Comparator**

When the SIO pin is configured as a differential input, it acts as a comparator. The reference generator block provides the threshold for the comparator. This comparator compares the input signal against the threshold voltage.

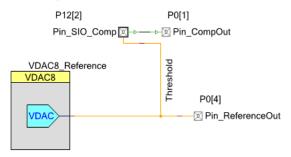

# **Top Design**

The Digital Input Pin component is placed on the top design and the input threshold is set to  $V_{\text{REF}}$  to enable external reference routing. This component is named as Pin\_SIO\_Comp. The VDAC output is connected to the reference terminal of SIO. The Digital Output Pin component is connected to the SIO input terminal and renamed as Pin\_CompOut. The analog pin Pin\_ReferenceOut is also connected to VDAC to see the reference.

In design wide resources (\*.cydwr) file, the pins Pin\_SIO\_Comp, Pin\_CompOut and Pin\_ReferenceOut are mapped to P12[2],P0[1], and P0[4] pins.

Figure 6. Top Design for Comparator

SIO as Comparator

# Digital Input Pin Configuration

Figure 7. Digital Input Pin Configuration

In the input tab, the threshold is set to  $V_{REF}$  and hysteresis is enabled. Hysteresis of  $\pm 50$  mV is provided on the SIO input buffer to remove the noise effects. The SIO\_HYST\_EN register enables the hysteresis individually for each SIO pin. See the TRM for more details.

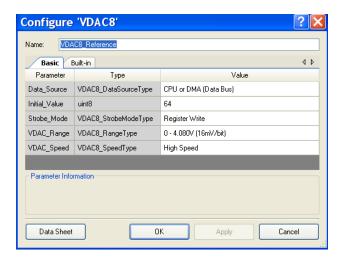

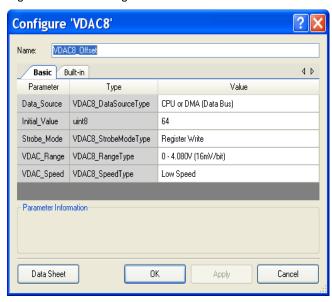

#### VDAC Configuration

The VDAC voltage is set to 1 V.

Figure 8. VDAC Configuration

The project details are as follows:

- Open the project SIO\_Comparator, build, and program the PSoC 3 / PSoC 5 on CY8CKIT-001 Development Kit.

- The ramp wave with amplitude 1 Vp-p and offset 1 V is given to P12[2].

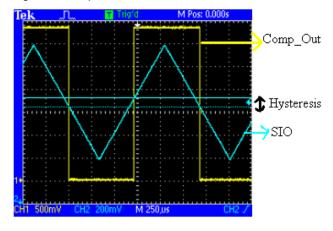

- 3. The comparator output is seen on pin P0[1]. Waveforms are shown in the following figure.

Figure 9. Comparator Waveforms

# **Tip 2: Comparator Wakeup**

The SIO comparator remains active in sleep and hibernate modes. It can be used to wake up the device from these modes to active mode. The reference signal from the comparator should be routed from external pins as the internal circuits are disabled in these modes.

**Note** The current with SIO comparator is around 100 µA.

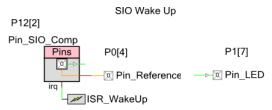

#### Top Design

The SIO is configured as comparator as shown in the previous example. The reference to SIO is given externally and this terminal is connected to analog pin named Reference. The interrupt on the rising edge is set in the SIO pin configuration. An Interrupt component is named ISR\_WakeUp and connected to the 'irq' terminal of SIO.

In design wide resources (\*.cydwr) file, the pins Pin\_SIO\_Comp, Pin\_Reference, and Pin\_LED are mapped to P12[2],P0[4], and P1[7] pins.

Also for device to go in sleep mode, the debug ports must be disabled. In the design wide resources (\*.cydwr) click on the system tab and disable the Debug Ports Select(DPS).

Figure 10. Comparator WakeUp

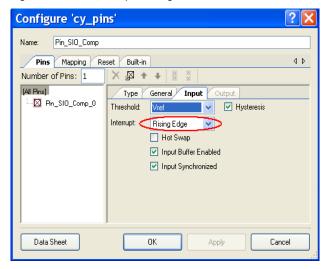

#### Configuration

The interrupt on SIO pin is set as rising edge interrupt.

Figure 11. SIO Interrupt Configuration

In the background loop, the device is put to sleep using CyPmSleep() API. When the SIO voltage crosses the reference, it generates rising edge at comparator output and wakes up the device from sleep. After wakeup, the device enters the ISR routine inside ISR and the interrupt flag is cleared. In the background loop, it toggles the pin Pin\_LED before going to sleep again. The same code can be written for the hibernate mode too using CyHibernate().

```

CyPmRestoreClocks();

/* When the device wakes up,

it toggles the LED */

Pin_LED_Write(Pin_LED_Read() ^

1);

/* Delays between next time

the device goes to sleep */

CyDelay(20);

}

```

The project details are as follows:

- 1. Open the project SIO\_WakeUp, build, and program the PSoC 3 / PSoC 5 on CY8CKIT-001 DVK.

- The potentiometer output VR (on P14 of DVK) is connected to P12[2]. Power the potentiometer by setting J11 to ON position.

- The VADJ on DVK is set to 1.5 V by varying adjustable resistor R11 on DVK. The VADJ (on P14 of DVK) is connected to P0[4].

- 4. P1[7] is connected to LED1.

- Vary the potentiometer VR on the DVK; whenever it crosses the 1.5 V the LED is toggled.

# Tip 3: Charge Pump

Charge pump is a kind of DC to DC converter that uses capacitors as energy storage elements to create a higher voltage power source.

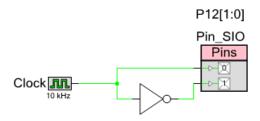

#### Top Design

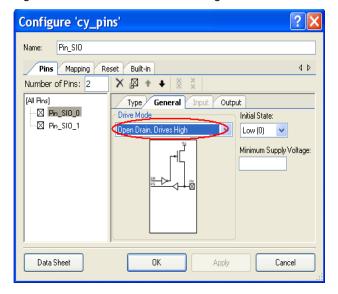

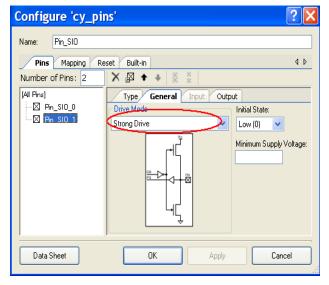

The Digital Output Pin component is placed in the top design, the number of pins is set to two, and the component is renamed as Pin\_SIO. The Pin\_SIO\_0 pin is configured as an Open Drain, Drive High and the Pin\_SIO\_1 is configured as a strong drive. A clock of 10 kHz is given to the input terminal of Pin\_SIO\_0 and the inverted clock is given to input terminal of Pin\_SIO\_1.

In design wide resources (\*.cydwr) file, these two SIO pins are mapped to P12[1:0] pins.

Figure 12. Top Design for SIO Charge Pump Charge Pump Using SIO

## Configuration

Figure 13. SIO Pins Drive Mode Configuration

#### Equivalent Schematic

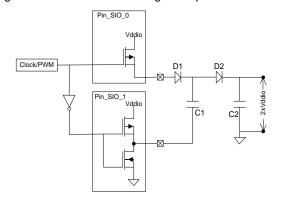

Connect an external capacitor to this SIO pair and make a circuit as follows.

Figure 14. Schematic for Charge Pump

The Pin\_SIO\_0 and Pin\_SIO\_1 pin drive mode configuration is as follows.

When the clock or PWM goes high, the Pin\_SIO\_0 charges the capacitor C1 to  $V_{DDIO}$  referenced against GND on the Pin\_SIO\_1. When the clock is low the Pin\_SIO\_0 is floating because of the open drain connection. But the low side of C1 is now  $V_{DDIO}$ , this makes C1 to have a 2 X  $V_{DDIO}$  voltage developed at its high side. This makes the diode to conduct and thus charges the capacitor C2 to 2 x  $V_{DDIO}$ . **Note** The capacitor C2 is referenced to GND and hence can see the entire voltage, 2  $V_{DDIO}$ .

This implements a charge pump to double the voltage. There is no need of diode D1 for voltage output up to 5 V because the SIO can withstand maximum of 5 V regardless of  $V_{\rm DDIO}$ . To achieve voltages higher than 5 V, the diode is used on the pin. PWM can also be used in place of the clock control. The PWM with a comparator feedback can achieve a feedback controlled voltage.

The project details are as follows:

- Open the project SIO\_ChargePump, build, and program the PSoC 3 / PSoC 5 on the CY8CKIT-001 (DVK).

- 2. The diodes and capacitors are connected as shown in Figure 14.

- The voltage of 2 x V<sub>DDIO</sub> is seen on the capacitor C2.

#### Tip 4: Level Shifter

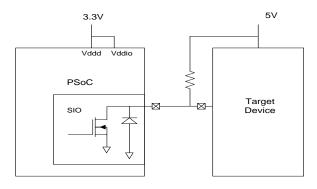

The SIO pins are tolerant to input voltages higher than the I/O supply voltage. The hot swap feature prevents input from being clamped to the I/O supply level, when the input voltage is above the I/O supply voltage. Each SIO pin can tolerate any input voltage up to 5 V, regardless of I/O supply voltage. In cases where the input voltage exceeds I/O supply voltage, the DC input leakage current is < 100  $\mu A$ . This feature allows the SIO to be connected to an external bus that can be switched to voltage levels higher than the I/O supply voltage.

The Digital Input Pin configuration enables Hot Swap feature is shown in Figure 15 on page 6

Figure 15. Hot Swap Configuration

Use the hot swap capability to interface to peripherals that operate at different voltage levels. The following example shows how to interface to peripheral operating at 5 V while the PSoC 3 / PSoC 5 device runs at 3.3 V. The SIO pin Drive Mode is configured to Open Drain, Drive Low mode.

Figure 16. Application using Hot Swap

Tip 5: Half Wave Rectifier

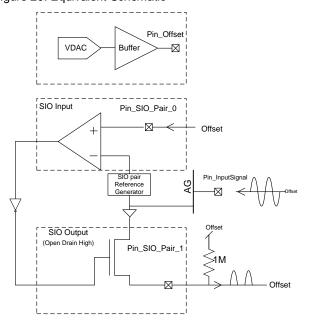

The half wave rectifier is achieved with a pair of SIO pins.

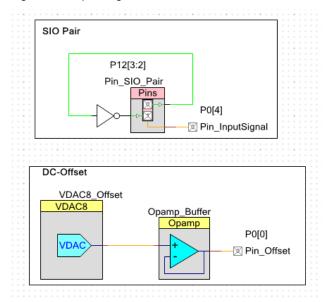

#### Top Design

The Digital Output Pin component is placed in the top design, the number of pins is set to two, and the component is renamed as Pin\_SIO\_Pair. The Pin\_SIO\_Pair\_0 pin is configured as input pin and the threshold is set to V<sub>REF</sub>. The Pin\_SIO\_Pair\_1 is configured as output pin, the Drive Level is set to 'V<sub>REF</sub>', and drive mode is set to Open Drain, Drive High. An analog pin is named as Pin\_InputSignal and connected to reference terminal of SIO. SIO\_Pair\_0 input terminal is inverted and then connected to the SIO\_pair\_1 output terminal.

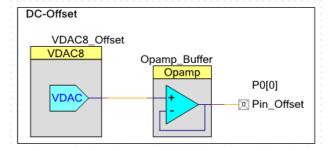

The VDAC component is placed and named to VDAC8\_Offset; it is set to give output of 1 V. The VDAC output is buffered using the opamp component; the opamp is named Opamp\_Buffer. The analog pin Pin\_Offset connected to the opamp, gives the DC offset for the input signal.

In design wide resources (\*.cydwr) file, the pins Pin\_SIO\_Pair[1:0], Input\_Signal, and Offset are mapped to P12[3:2], P0[4], and P0[0] pins.

Figure 17. Top Design for Half Wave Rectifier

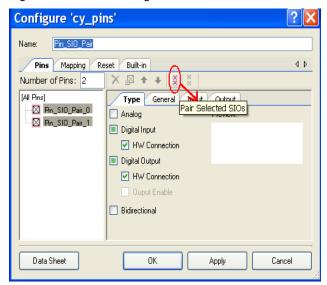

#### Pairing SIO pins

To map the pins as SIO pair, click on [All Pins] and select 'Pair Selected SIOs' option.

Figure 18. SIO Pair Configuration

Figure 19. DAC Configuration

#### Equivalent Schematic

Figure 20. Equivalent Schematic

The analog input signal is biased on the offset and is given to SIO reference terminal. The Pin\_SIO\_Pair\_0 is connected to offset voltage. Whenever the signal is in positive half cycle the SIO\_Pair\_0 input is logic 'Low'. This input is inverted and used to drive the other SIO pin Pin\_SIO\_Pair\_1. The Pin\_SIO\_Pair\_1 gives the reference as output as it is configured in regulated mode. Thus in positive half cycle of the input signal, the output of the SIO\_Pair\_Ref is the signal itself. For negative cycle, the Pin\_SIO\_Pair\_1 outputs High-Z as it is configured in Open Drain, Drive High configuration. The pull up resistor is connected to make the output equal to Offset during negative cycles.

**Note** The signal should be less than  $V_{DDIO}/2$  because the maximum limit on the SIO input threshold in differential mode is  $V_{DDIO}/2$ .

The project details are as follows:

- Open the project 'SIO\_HalfWaveRectifier', build, and program the PSoC 3 / PSoC 5 on the CY8CKIT-001 DVK.

- The analog signal is given to pin P0[4] with respect to P0[0]. This makes the input signal biased at 'Offset'.

- 3. Connect offset voltage P0[0] to P12[2].

- 4. The pull up resistor of 1 M is connected between P12[3] and P0[0].

- Observe the half wave rectified output on pin P12[3].

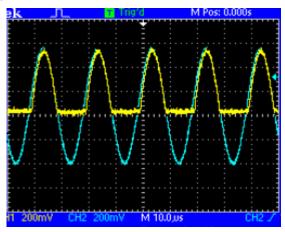

Waveforms: At 50 kHz, with input 1V p-p.

Figure 21. Waveforms for Half Wave Rectifier

#### **Tip 6: Peak Detector**

This section explains how a single SIO can function as a peak detector of an analog signal. It gives the digital signal with transitions at the peaks of the analog signal. The analog signal amplitude level should be less than  $V_{\rm DDIO}/2$  peak to peak, because threshold of SIO should be less than  $V_{\rm DDIO}/2$ .

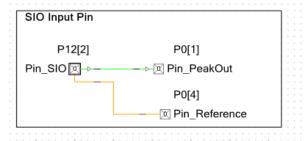

#### Top Design

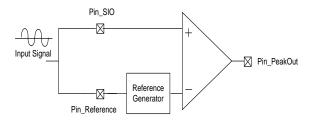

The Digital Input Pin is placed in the top design; the threshold is set to  $V_{REF}$  and the pin is named as 'Pin\_SIO'. The Reference terminal of the SIO is connected to the analog pin named Pin\_Reference.

The VDAC component is placed and named to 'VDAC8\_Offset'; it is set to give output of 2 V. The VDAC output is buffered using the opamp component; the opamp is named Opamp\_Buffer. The analog pin Pin\_Offset connected to the opamp, gives the DC offset for the input signal.

In design wide resources (\*.cydwr) file, the pins Pin\_SIO, Pin\_Reference, Pin\_PeakOut, and Pin\_Offset are mapped to P12[2], P0[4], P0[1] and P0[0] pins.

Figure 22. Top Design for Peak Detector

## Equivalent Schematic

Figure 23. Equivalent Schematic

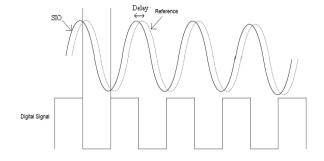

The analog signal is biased at the Offset voltage. This signal is connected to both the SIO pin and also to the reference of the SIO. The reference of SIO goes to the reference generator and it experiences a small delay in reaching the threshold input of the comparator. This delay between the SIO input and the reference input makes it a peak detector. The input signal is compared at the SIO input buffer against the delayed version of the signal and the comparator output crosses zero at the peaks, as shown in Figure 24.

Figure 24. Waveforms Showing Input and Delayed Signals

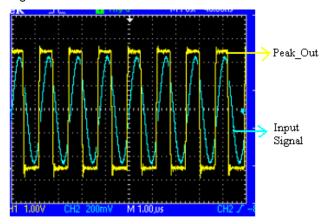

The project details are as follows:

- Open the project SIO\_PeakDetector, build, and program the PSoC 3 / PSoC 5 on the CY8CKIT-001 DVK.

- 2. The analog signal is biased on P0[0] and given to both P12[2] and P0[4].

- 3. The digital output is seen on the pin P0[1].

- 4. Waveforms are shown in the following figure.

The input signal is at 800 kHz, 1 Vpp and offset is 2 V. The  $V_{\rm DDIO}$  = 5 V.

Figure 25. Peak Detector Waveforms

Tip 7: SIO as SPST/SPDT Switch

The SIO can be used as a hardware analog switch.

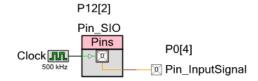

#### Top Design

The Digital Output Pin is placed in the Top Design. The drive level is set to  $V_{REF}$  and the pin is named as Pin\_SIO. An analog pin named as 'Pin\_InputSignal' is connected to SIO's Reference terminal. The clock component is set to frequency 500 kHz and connected to output terminal of SIO.

In design wide resources (\*.cydwr) file, the pins Pin\_SIO and Pin\_InputSignal are mapped to P12[2] and P0[4] pins.

Figure 26. Top Design for SIO Switch

# SIO as a switch

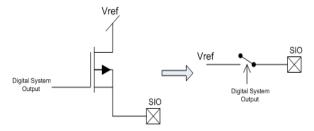

Single Pole Single Throw switch (SPST): SIO pin drive mode is configured as Open Drain, Drives High. The digital output to the SIO connects/disconnects the  $V_{\text{REF}}$  and SIO pin.

Figure 27. Equivalent Circuit for SPST Switch

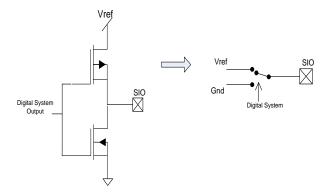

Single Pole Double Throw (SPDT): SIO pin drive mode is configured as Strong Drive. The digital output to the SIO connects or disconnects the SIO pin between  $V_{\text{REF}}$  and Gnd.

Figure 28. Equivalent Circuit for SPDT Switch

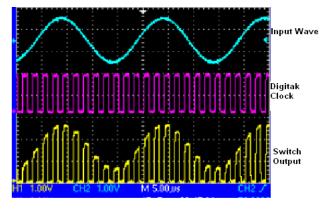

The project details are as follows:

- Open the project 'SIO\_Switch', build, and program the PSoC 3 / PSoC 5 on the CY8CKIT-001 DVK.

- 2. The input signal is given to P0[4].

- The output, which is switched at 500 kHz is seen at P12[2]. The output of P12[2] switches between signal and ground giving the SPDT functionality.

- 4. Waveforms are shown in the following figure.

A clock of 500 kHz is made to drive the SIO pin configured in 'Strong Drive' mode.

Figure 29. Waveforms showing SIO Switch

# Summary

The SIO pin on PSoC 3 / PSoC 5 is designed to perform some special tasks. These are level translator, hot swap capability, and high current capability as explained in PSoC Creator configuration section. However, the SIO pin is so resourceful and flexible that many designs can be accomplished with this, making it a powerful feature. Thus, it is useful to consider how to exploit the features of the SIO in every design.

# **Document History**

Document Title: SIO Tips and Tricks in PSoC® 3 / PSoC 5

Document Number: 001-60580

| Revision | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                     |

|----------|---------|--------------------|--------------------|-----------------------------------------------------------------------------------------------------------|

| **       | 2901596 | PVKV               | 03/30/2010         | New Application Note                                                                                      |

| *A       | 2967030 | PVKV               | 07/01/2010         | Updated for PSoC Creator 4.1, updated the project and document to work with PSoC 3 / PSoC 5.              |

| *B       | 3013833 | PVKV               | 08/23/2010         | The API Cy_Sleep() is changed to Cy_pm_Sleep(). TIP 2: Comparator Wakeup updated according to a new code. |

PSoC is a registered trademarks and PSoC Creator is a trademark of Cypress Semiconductor Corp. All other trademarks or registered trademarks referenced herein are the property of their respective owners.

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709 Phone: 408-943-2600 Fax: 408-943-4730 http://www.cypress.com/

© Cypress Semiconductor Corporation, 2010. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

This Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.