# Datapath Configuration Tool Cheat Sheet

This document tells you all you need to know about the Datapath Configuration Tool to configure datapaths.

# **Contents**

| Datapath Configuration Tool Introduction   | 2  |

|--------------------------------------------|----|

| Dynamic Configuration RAM (CFGRAM) Section | 4  |

| Static Configuration Section               | 7  |

| CFG9 Register                              | 7  |

| CFG11 and CFG10 Registers                  | 8  |

| CFG13 and CFG12 Registers                  | 9  |

| CFG15 and CFG14 Registers                  | 10 |

| CFG17 and CFG16 Registers                  | 12 |

| Setting Initial Register Values            | 14 |

| Datapath Chaining                          | 14 |

| Firmware-Control of Datapath Registers     | 16 |

| Miscellaneous                              | 17 |

### **Datapath Configuration Tool Introduction**

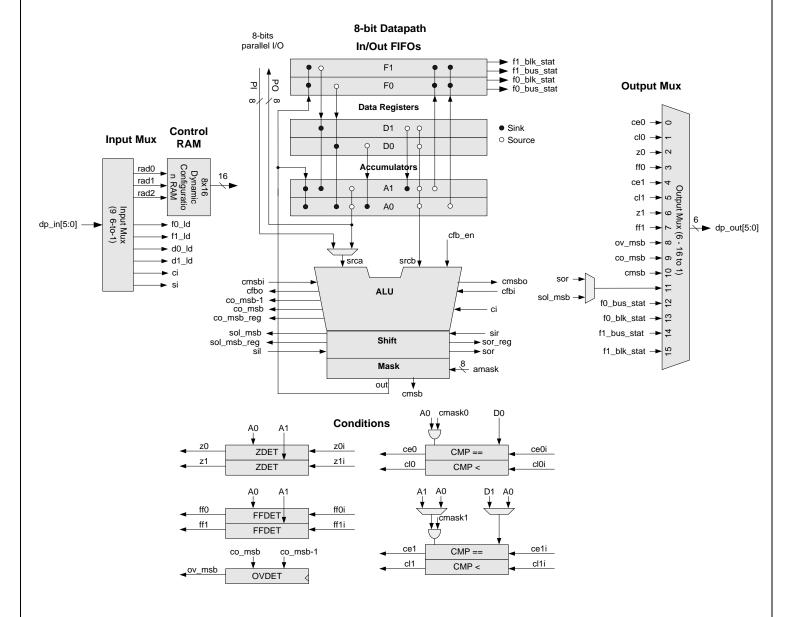

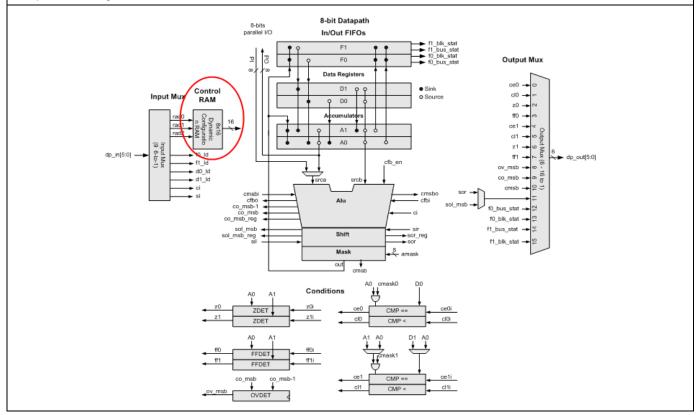

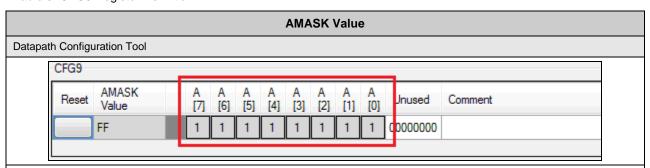

The Datapath is an 8-state state machine, while the Datapath Configuration Tool (DCT) is a bit-banger made easy through a GUI. This document shows the relationship between the DCT and the underlying Datapath hardware.

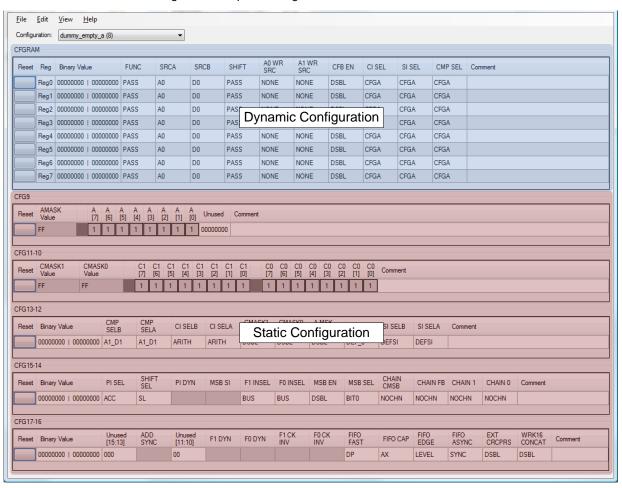

The GUI can be divided into two general sections – the Dynamic Configuration and Static Configuration sections, as Figure 1 shows.

- Dynamic Configuration Allows you to set up the Datapath to behave differently across states

- Static Configuration Stays the same across states

Figure 1. Datapath Configuration Tool Interface Sections

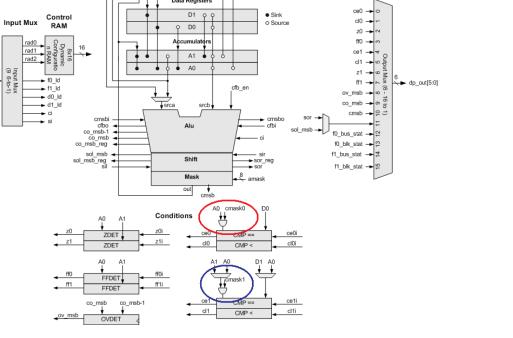

Figure 2. Datapath Block Diagram

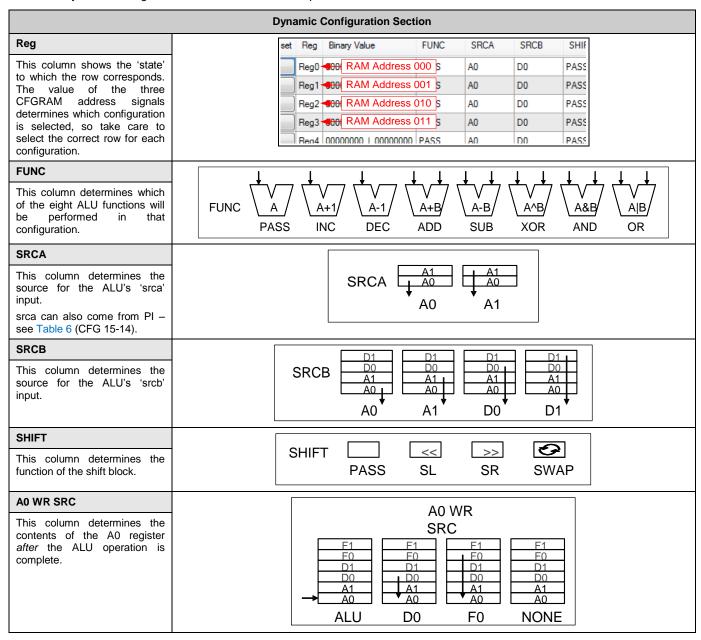

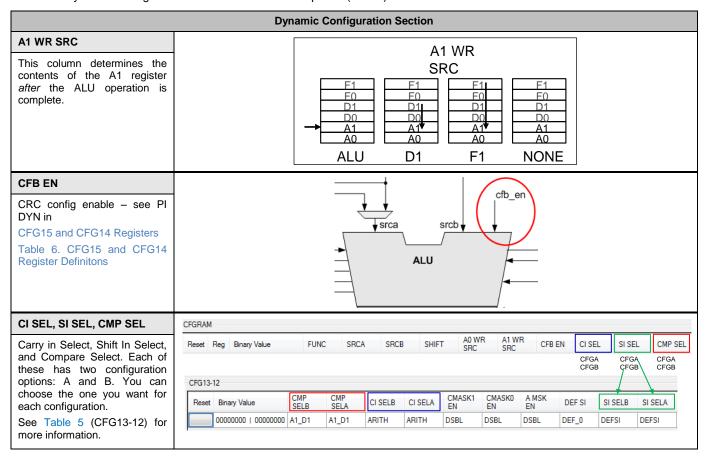

### **Dynamic Configuration RAM (CFGRAM) Section**

The Dynamic Configuration section is a representation of the configuration RAM. It configures the behavior of the datapath in the 8 'states' of the state machine. The following tables explain the function of each of the fields in the GUI.

Table 1. The CFGRAM Section of the Datapath Configuration Tool

| Dynamic Configuration RAM Section |      |                     |      |      |      |       |              |              |        |        |        |         |

|-----------------------------------|------|---------------------|------|------|------|-------|--------------|--------------|--------|--------|--------|---------|

| atapath Configuration Tool        |      |                     |      |      |      |       |              |              |        |        |        |         |

| CFGRA                             | М    |                     |      |      |      |       |              |              |        |        |        |         |

| Reset                             | Reg  | Binary Value        | FUNC | SRCA | SRCB | SHIFT | A0 WR<br>SRC | A1 WR<br>SRC | CFB EN | CI SEL | SI SEL | CMP SEL |

|                                   | Reg0 | 00000000   00000000 | PASS | A0   | D0   | PASS  | NONE         | NONE         | DSBL   | CFGA   | CFGA   | CFGA    |

|                                   | Reg1 | 00000000   00000000 | PASS | A0   | D0   | PASS  | NONE         | NONE         | DSBL   | CFGA   | CFGA   | CFGA    |

|                                   | Reg2 | 00000000   00000000 | PASS | A0   | D0   | PASS  | NONE         | NONE         | DSBL   | CFGA   | CFGA   | CFGA    |

|                                   | Reg3 | 00000000   00000000 | PASS | A0   | D0   | PASS  | NONE         | NONE         | DSBL   | CFGA   | CFGA   | CFGA    |

|                                   | Reg4 | 00000000   00000000 | PASS | A0   | D0   | PASS  | NONE         | NONE         | DSBL   | CFGA   | CFGA   | CFGA    |

|                                   | Reg5 | 00000000   00000000 | PASS | A0   | D0   | PASS  | NONE         | NONE         | DSBL   | CFGA   | CFGA   | CFGA    |

|                                   | Reg6 | 00000000   00000000 | PASS | A0   | D0   | PASS  | NONE         | NONE         | DSBL   | CFGA   | CFGA   | CFGA    |

|                                   | Reg7 | 00000000   00000000 | PASS | A0   | D0   | PASS  | NONE         | NONE         | DSBL   | CFGA   | CFGA   | CFGA    |

#### Datapath Block Diagram

Table 2. Dynamic Configuration Section Column Descriptions

Table 2. Dynamic Configuration Section Column Descriptions (contd.)

### **Static Configuration Section**

The Static Configuration section represents the datapath registers CFG9 to CFG17, as Table 3, Table 4, Table 5, Table 6, and Table 7 show. They control static functions, including shift direction, masking, FIFO configuration, and chaining.

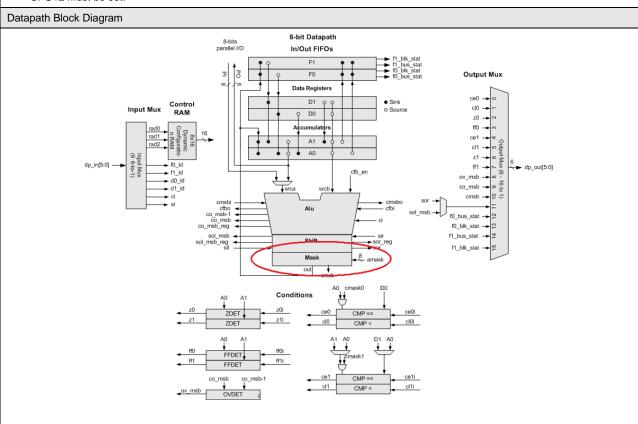

### **CFG9 Register**

Table 3. CFG9 Register Definition

AMASK Value – This field contains the 8-bit mask value that is applied to the output of the Datapath ALU block. The output of

the shift register is ANDed with the contents of this register. This feature is off by default. To enable it the AMASK EN bit

CFG12 must be set.

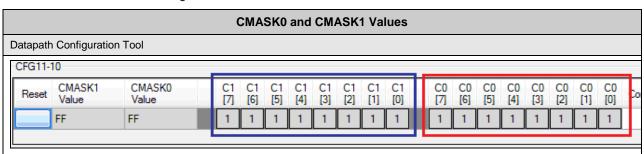

### CFG11 and CFG10 Registers

dp\_in[5:0] -

Table 4. CFG11 and CFG10 Register Definitions

CMASK0 and CMASK1 – These fields set the mask values used with the comparator block inputs. The contents of the A0 or A1 register are ANDed with the contents of these registers before comparison. To enable them, the CMASK0 EN and CMASK1 EN bits must be set in CFG12 (Table 5).

###

## CFG13 and CFG12 Registers

Table 5. CFG13 and CFG12 Register Definitions

|                                                                                                                                       | o. CFG 13 and CFG                                                                                                                            |                                                         |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |                      |                      |             |                           |                  |         |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------|----------------------|-------------|---------------------------|------------------|---------|--|--|

|                                                                                                                                       |                                                                                                                                              |                                                         | C                          | FG13-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Configura                | tion Selec           | tions                |             |                           |                  |         |  |  |

| Datapatl                                                                                                                              | h Configuration Tool                                                                                                                         |                                                         |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |                      |                      |             |                           |                  |         |  |  |

| -CFG13-                                                                                                                               | -12                                                                                                                                          |                                                         |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |                      |                      |             |                           |                  |         |  |  |

| Reset                                                                                                                                 | Binary Value                                                                                                                                 | CMP<br>SELB                                             | CMP<br>SELA                | CI SELB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CI SELA                  | CMASK1<br>EN<br>DSBL | CMASK0<br>EN<br>DSBL | A MSK<br>EN | DEF SI                    | SI SELB<br>DEFSI | SI SELA |  |  |

|                                                                                                                                       | 00000000   00000000                                                                                                                          | A1_D1                                                   | A1_D1                      | ARITH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ARITH                    |                      |                      | DSBL        | DEF_0                     |                  | DEFSI   |  |  |

|                                                                                                                                       |                                                                                                                                              |                                                         |                            | C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | FG13-12 D                | etails               |                      |             |                           |                  |         |  |  |

| Configure Compariblock 1. configure option is Note: C                                                                                 | res the Comparison A Options for The CMP SEL field ation determines if it is in effect for a given compare block 0 called and a masked value | r compai<br>of the RA<br>the A or<br>cycle.<br>n compai | d A1_A<br>e A0_D<br>M A0_A | 11: A1 < D<br>0: A1 < A<br>11: A0 < D<br>0: A0 < A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0, A1 == A<br>1, A0 == [ | \0<br>D1             |                      | ce1         | A0 D1 Pmask1 CMP == CMP < | ceti<br>cl1i     |         |  |  |

| CI SELE                                                                                                                               | 3 & CI SEL A                                                                                                                                 |                                                         | ARIT                       | ARITH: The carry is controlled by ALU arithmetic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                          |                      |                      |             |                           |                  |         |  |  |

| Selects the source of the carry in.                                                                                                   |                                                                                                                                              |                                                         |                            | REGIS: The carry in is carry out registered from previous cycle.  ROUTE: Carry in is selected from one of the datapath inputs.  CHAIN: Carry in is driven from previous datapath in chain.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |                      |                      |             |                           |                  |         |  |  |

| Enables and Corand the                                                                                                                | the Masks on the ompare 0 Blocks (sh<br>Mask block at the or<br>ot shown). See Ta                                                            | Compare nown righ                                       | 1<br>t)<br>e               | A1 A0 D1 A0    Compask   C |                          |                      |                      |             |                           |                  |         |  |  |

| DEF SI                                                                                                                                |                                                                                                                                              |                                                         | DEF_                       | DEF_0: Zero                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          |                      |                      |             |                           |                  |         |  |  |

| value is                                                                                                                              | whether the defar<br>a 0 or a 1. Note SI a<br>nust be set to DEFS                                                                            | SELB or S                                               | SI -                       | DEF_1: One                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |                      |                      |             |                           |                  |         |  |  |

| SI SELE                                                                                                                               | 3 & SI SEL A                                                                                                                                 |                                                         | DEFS                       | <b>DEFSI:</b> Shifts in either a zero or a one, as defined by DEF SI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                          |                      |                      |             |                           |                  |         |  |  |

| Selects the source of the shift in for the A and B shift in configuration.  REGIS: Shift in is ROUTE: Shift in it CHAIN: Shift in its |                                                                                                                                              |                                                         |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          | d from a d           | latapath in          | out.        |                           |                  |         |  |  |

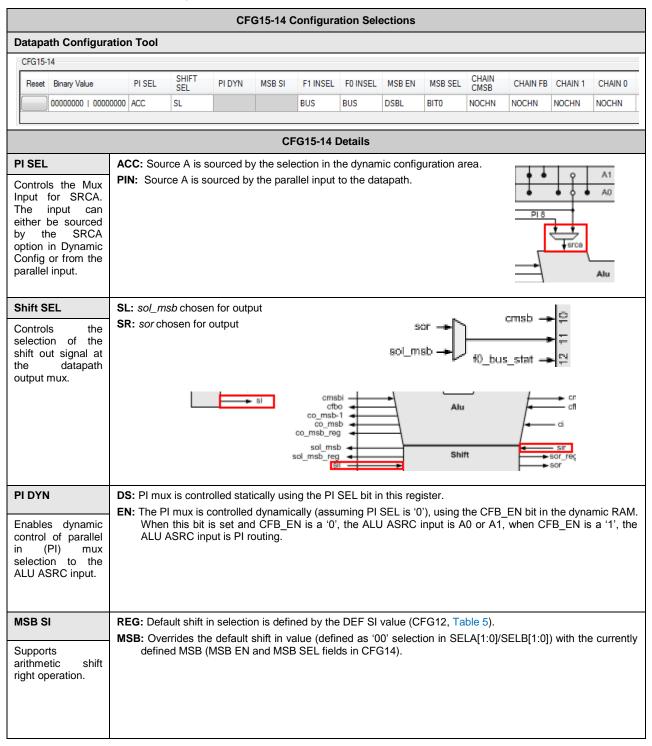

### CFG15 and CFG14 Registers

Table 6. CFG15 and CFG14 Register Definitons

#### CFG15-14 Details (contd.) F1 INSEL & F0 INSEL Bus: FIFO input is the CPU bus, FIFO ALU A1 output is A0 or D0 Defines the input source of Registers FIFO 1 and FIFO 0. A0: FIFO input is A0. FIFO Output is CPU BUS. A1: FIFO input is A1. UDB B FIFO Output is CPU BUS. Local ALU: FIFO input is the ALU. FIFO Output is CPU BUS. FIFO F0 FIFO F1 ┏ MSB EN and MSB SEL When the MSbit is Default (tie value) shift in left (sil) changed Registered (sor\_reg) anything other You can adjust the MSbit of the Routed (from interconnect) Selected MSB than bit 7, the shift ALU output. These two settings in, shift out, and Chained (from next Datapath) allow you to disable and carry out outputs enable this feature and choose change which bit is the MSbit. accordingly. shift out left (sol\_msb) (to DP output mux) sol\_msb\_reg co\_msb (to DP output mux) co\_msb\_reg **Chain CMSB** The CRC MSB signal flow is from MS block to LS block. Set this bit when this Datapath does not contain the most significant bit of a CRC computation. Enables chaining from the next NOCHN: CRC MSB is not chained. Datapath in the chain to this CHNED: Chain the CRC MSB from the next Datapath block in the chain. block for the CRC MSB. Chain FB The CRC FB signal flow is from LS block to MS block. Set this bit when this Datapath does not contain the least significant bit of a CRC computation. Enables chaining from the NOCHN: CRC feedback is not chained. previous Datapath in the chain to this block for the CRC CHNED: CRC feedback is chained from the previous Datapath block in the chain. feedback. Chain 1 & Chain 0 When set to chained (CHNED), the conditions from the previous datapath are chained to this datapath. Chain 0 affects CL0, CE0, Z0, and FF0 conditions. Chain 1 affects CL1, CE1, Z1, and Defines whether the outputs of FF1 conditions. CL0, CL1, CE0, CE1, Z0, Z1, FF0, and FF1 are chained.

#### CFG17 and CFG16 Registers

### Table 7. CFG17 and CFG16 Register Definitions

| FIFO Configurations         |                   |             |                   |        |        |              |              |              |          |              |               |               |                 |

|-----------------------------|-------------------|-------------|-------------------|--------|--------|--------------|--------------|--------------|----------|--------------|---------------|---------------|-----------------|

| Datapath Configuration Tool |                   |             |                   |        |        |              |              |              |          |              |               |               |                 |

| CFG17-16                    |                   |             |                   |        |        |              |              |              |          |              |               |               |                 |

| Reset Binary Value          | Unused<br>[15:13] | ADD<br>SYNC | Unused<br>[11:10] | F1 DYN | F0 DYN | F1 CK<br>INV | F0 CK<br>INV | FIFO<br>FAST | FIFO CAP | FIFO<br>EDGE | FIFO<br>ASYNC | EXT<br>CRCPRS | WRK16<br>CONCAT |

| 00010000   00000000         | 000               | ADD         | 00                |        |        |              |              | DP           | AX       | LEVEL        | SYNC          | DSBL          | DSBL            |

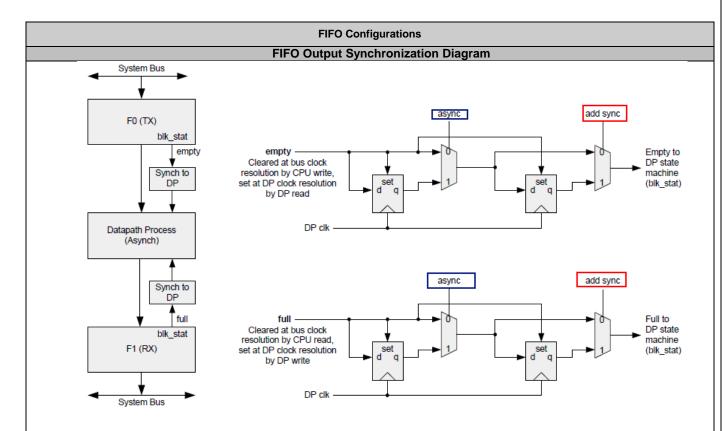

■ ADD SYNC – Determines whether an additional sync flip-flop is added to the FIFO block status. This controls the cycle timing between bus reads/writes at bus clock resolution, and the assertion of the new status on Datapath output routing. There is only one configuration bit that controls this for both FIFOs. See the FIFO Configurations section on the next page.

NONE: Does not add a flip-flop to the output of the FIFO block status.

ADD: Adds a flip-flop to the output of the FIFO block status.

■ F1 DYN — Controls whether the FIFO1 direction is static or dynamic. In static mode, the F1\_SEL[1:0] bits control the FIFO read and write access. When this bit is set for dynamic mode there are two configurations: internal access, where the FIFO can be read and written to by the Datapath, and external access, where the FIFO can be read and written to by the system bus. In this mode, the F1\_SEL[1:0] bits control the FIFO write source in internal access mode.

OFF: Static Mode. FIFO direction is static and controlled by F1\_SEL[1:0].

ON: Dynamic Mode. FIFO direction is dynamic and controlled between internal and external access by toggling the DP routed signal d1 load.

- F0 DYN Read description for F1 DYN

- F0 CLK INV and F1 CLK INV Determine whether the FIFO clock is inverted relative to the datapath clock.

**NEG**: FIFO clock is the same polarity as the DP clock

POS: FIFO clock is inverted with respect to the DP clock

■ FIFO FAST – Determines whether the FIFOs are clocked using the Datapath clock or the PSoC Bus Clock. In fast mode, the FIFO is clocked by the bus clock, which reduces capture latency.

The use of this mode results in slightly higher power consumption because the master and quadrant gating of bus clock must be enabled. This bit controls the mode for both FIFOs in the UDB, but it only applies to FIFOs that are configured in output mode.

DP: Datapath Clock

BUS: Bus Clock

■ FIFO CAP – Enables FIFO capture mode. If enabled, a read of A0 or A1 will write into F0 or F1, respectively.

AX: A read of A0 or A1 returns the value in the register directly.

FX: A read of A0 (or A1) triggers a capture into F0 (or F1).

■ FIFO EDGE – Determines whether FIFO writes occur on a LOW to HIGH transition. Or, if they can occur at any time, the F0 or F1 load signal is HIGH.

**LEVEL**: A FIFO write (output mode) is level sensitive.

**EDGE**: A FIFO write (output mode) is edge sensitive.

■ FIFO ASYNC – Determines if a flip-flop is needed on the output of the FIFO block status signals. See the FIFO Configurations section on the next page.

SYNC: Does not add a flip-flop at the output of the FIFO block status.

**ASYNC:** Adds a flip-flop to the output of the FIFO block status. Setting ADD SYNC to *NONE* and FIFO ASYNC to *ASYNC* or ADD SYNC to *ADD* and FIFO ASYNC to *SYNC* is acceptable only if the Datapath clock has been synchronized to MASTER\_CLK.

■ EXT CRCPRS – Overrides the internal configuration for CRC/PRS calculation and allows external routing of CRC/PRS signals. When this bit is set, access is given to the raw block inputs for the CRC operation, including the shift in data and the feedback data, and calculations for these signals must be done externally. (Typically in the PLD).

**DSBL**: Internal CRC/PRS routing

ENBL: External CRC/PRS routing.

■ WRK16 CONCAT – Controls the working register access mode in the 16-bit access space. By default, when this bit is a '0' the access occurs the same register across a pair of UDBs in chaining order. When this bit is set to '1', a 16-bit read or write accesses concatenated registers within a single UDB. The combinations are {A1,A0}, {D1,D0}, F1,F0}, {CTL,STAT},{MSK, ACTL}, {8'b0,MC}.

DSBL: 16-bit Default Access Mode. A 16-bit access reads/writes a given register in two consecutive UDBs in chain/address order.

ENBL: 16-bit Concat Access Mode. A 16-bit access reads/writes concatenated registers in a single UDB.

| ASYNC | ADD SYNC | Operation                                   | Usage Model                                                                                                                                                                                                                  |

|-------|----------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | 0        | Synchronous to<br>Bus clock                 | CPU read/write status changes occur at bus clock resolution. Can be used for minimum latency if the bus clock timing can be met.                                                                                             |

| 0     | 1        | Re-sampled from<br>Bus Clock to DP<br>Clock | This should be the default synchronous operating mode. When the CPU read/write status changes are synchronously re-sampled with the currently selected DP clock. Gives a full cycle of DP clock setup time to the UDB logic. |

| 1     | 0        | (redundant)                                 |                                                                                                                                                                                                                              |

| 1     | 1        | Double Synced from Bus Clock to DP Clock    | When a free running asynchronous DP clock is in use, this setting can be used to double sync the CPU read and write actions to the DP clock.                                                                                 |

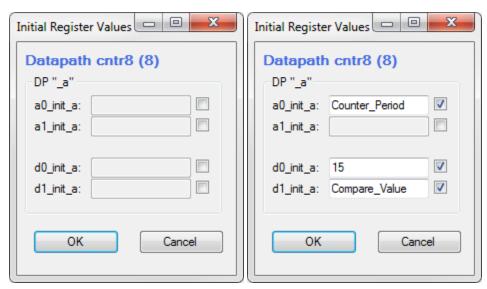

### **Setting Initial Register Values**

To set the initial values of A0, A1, D0, D1 in the DCT, go to View>Initial Register Values. Say the Datapath name is Cntr8, the window would look like Figure 3 (left).

Figure 3. Initial Register Value

You can set the initial values by clicking on the checkboxes and entering either a number or a valid parameter name from the destination Verilog file (Figure 3 right).

### **Datapath Chaining**

Dedicated Datapath chaining signals allow efficient implementation of single-cycle 16-, 24-, and 32-bit bit functions without the use of channel routing resources.

As shown in Figure 4, all generated conditional and capture signals chain in the direction of least significant to the most significant blocks. Shift left also chains from least to most significant. Shift right chains from most significant to least significant. The CRC/PRS chaining signals of CFBO (feedback) chain least to most, but the CMSBO (MSB output) chains from most to least significant.

UDB c UDB b UDB a CE0 CE0i CE0 CE0 CE0i CE0i CL0 CL0i CL0 CL0i CL0 CL0i CE1 CE1i CE1 CE1i CE1 CE1i CL1 CL1 CL1 CL1i CL1i CL1i Z0 Z0i Z0 Z0i Z0 Z0i Z1 Z1i Z1 Z1i Z1 Z1i FF0 FF0i FF0 FF0i FF0 FF0i FF1 FF1i FF1 FF1i FF1 UDB2 UDB1 UDB0 CAP0 CAP0i CAP0 CAP0i CAP0 CAP0i CAP1 CAP1i CAP1 CAP1i CAP1 CAP1i CO\_MSB CI CO\_MSB CI CO\_MSB CI SOL\_MSB SIR SOL MSB SIR SOL MSB SIR **CFBO** CFBI **CFBO** CFBO **CFBI CFBI** 0 -SIL SOR SIL SOR SIL SOR CMSBI CMSBO CMSBI CMSBO **CMSBO**

Figure 4. Datapath Chaining Signal Flow

Figure 5 shows the settings required for chaining Datapaths for various cases. UDB\_a is the least significant block, while UDB\_c is the most significant block. Figure 5 describes a 3 UDB (up to 24-bit) function; a 16-bit or 32-bit function can be created by removing or duplicating the middle Datapath configuration. The figure shows configuration for Chain FB and Chain CMSB even though they may not be used.

Keeping Figure 4 in mind, when chaining together Datapaths, a majority of designs (for example, simple adding or subtracting) would use the 'Basic Configuration' row in Figure 5, that is, chain all signals from LSB (UDB\_a) to MSB (UDB\_c) except for Chain CMSB. If you perform any shift operations, based on the direction of shift, you need to change the shift chaining configuration – shown in the Shift Left, Shift Right and Arithmetic Shift Right rows in Figure 5.

Figure 5. DCT Configuration for Chaining

|                           | UDB_c                                                                                        | UDB_b                                                                                     | UDB_a                                                                               |

|---------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| Basic<br>Configuration    | CI SELx: CHAIN<br>CHAINx: CHAIN<br>Chain FB: CHAIN<br>Chain CMSB: NO CHAIN                   | CI SELx: CHAIN<br>CHAINx: CHAIN<br>Chain FB: CHAIN<br>Chain CMSB: CHAIN                   | CI SELx: ARITH<br>CHAINx: NO CHAIN<br>Chain FB: NO CHAIN<br>Chain CMSB: CHAIN       |

|                           | UDB_c                                                                                        | UDB_b                                                                                     | UDB_a                                                                               |

| Shift Left                | CI SELx: CHAIN<br>CHAINx: CHAIN<br>Chain FB: CHAIN<br>Chain CMSB: NO CHAIN<br>SI SELx: CHAIN | CI SELx: CHAIN<br>CHAINx: CHAIN<br>Chain FB: CHAIN<br>Chain CMSB: CHAIN<br>SI SELx: CHAIN | CI SELx: ARITH CHAINX: NO CHAIN Chain FB: NO CHAIN Chain CMSB: CHAIN SI SELx: DEFSI |

|                           | UDB_c                                                                                        | UDB_b                                                                                     | UDB_a                                                                               |

| Shift Right               | CI SELx: CHAIN CHAINx: CHAIN Chain FB: CHAIN Chain CMSB: NO CHAIN SI SELx: DEFSI             | CI SELx: CHAIN CHAINX: CHAIN Chain FB: CHAIN Chain CMSB: CHAIN SI SELx: CHAIN             | CI SELX: ARITH CHAINX: NO CHAIN Chain FB: NO CHAIN Chain CMSB: CHAIN SI SELX: CHAIN |

|                           | UDB_c                                                                                        | UDB b                                                                                     | UDB_a                                                                               |

| Arithmetic<br>Shift Right | CI SELx: CHAIN CHAINx: CHAIN Chain FB: Chain Chain CMSB: NO CHAIN  SI SELx: DEFSI MSB SI:MSB | CI SELx: CHAIN CHAINx: CHAIN Chain FB: Chain Chain CMSB: CHAIN SI SELx: CHAIN             | CI SELx: CHAIN CHAINx: CHAIN Chain FB: No Chain Chain CMSB: CHAIN SI SELx: CHAIN    |

### **Firmware-Control of Datapath Registers**

The Datapath registers can be accessed in firmware by using the macros CY\_SET\_REG8(addr, value) and CY\_GET\_REG8(addr), or the corresponding 16-, 24-, or 32-bit versions of these functions as the case may be.

The address of the registers can be found in the cyfitter.h file (generated after a successful build). For example, if the 8-bit Datapath instance named cntr8 is instantiated in a component named SimpleCntr8\_1, the cyfitter.h file contains a block of code which lists the addresses of all the Datapath registers Figure 6.

```

/* SimpleCntr8 1 */

#define SimpleCntr8 1 cntr8 u0 16BIT A0 REG CYREG B1 UDB05 06 A0

#define SimpleCntr8 1 cntr8 u0 16BIT A1 REG CYREG B1 UDB05 06 A1

#define SimpleCntr8_1_cntr8 u0 16BIT D0 REG CYREG B1 UDB05 06 D0

#define SimpleCntr8 1 cntr8 u0 16BIT D1 REG CYREG B1 UDB05 06 D1

#define SimpleCntr8 1 cntr8 u0 16BIT DP AUX CTL REG CYREG B1 UDB05 06 ACTL

#define SimpleCntr8 1 cntr8 u0 16BIT F0 REG CYREG B1 UDB05 06 F0

#define SimpleCntr8 1 cntr8 u0 16BIT F1 REG CYREG B1 UDB05 06 F1

#define SimpleCntr8 1 cntr8 u0 A0 A1 REG CYREG B1 UDB05 A0 A1

#define SimpleCntr8 1 cntr8 u0 A0 REG CYREG B1 UDB05 A0

#define SimpleCntr8 1 cntr8 u0

A1 REG CYREG B1 UDB05 A1

#define SimpleCntr8 1 cntr8 u0

DO D1 REG CYREG B1 UDB05 D0 D1

#define SimpleCntr8 1 cntr8 u0

DO REG CYREG B1 UDB05 D0

#define SimpleCntr8 1 cntr8 u0

D1 REG CYREG B1 UDB05 D1

#define SimpleCntr8 1 cntr8 u0

DP AUX CTL REG CYREG B1 UDB05 ACTL

#define SimpleCntr8 1 cntr8 u0

FO F1 REG CYREG B1 UDB05 F0 F1

#define SimpleCntr8 1 cntr8 u0

FO REG CYREG B1 UDB05 F0

#define SimpleCntr8 1 cntr8 u0

F1 REG CYREG B1 UDB05 F1

```

Figure 6. Addresses of Datapath Registers

#### **Miscellaneous**

For more information about the Datapath Configuration Tool, see Appendix B of the Component Author Guide, available in the DCT under **Help>Documentation**, or in PSoC Creator under **Help>Documentation>Component Author Guide**.