# Advantages of 65 nm Technology over 90 nm Technology QDR<sup>®</sup> Family of SRAMs

## AN58815

Author: Jayasree Navar

**Associated Project: No**

Associated Part Family: CY7C13xxKV18, CY7C14xxKV18

CY7C15xxKV18, CY7C25xxKV18

Software Version: None

**Associated Application Notes: None**

### **Application Note Abstract**

This application note outlines the advantages of the 65 nm technology QDR® SRAMs over the 90 nm technology SRAM devices.

#### Introduction

# **Overview** The 65 nm technology QDR family of devices offers

significant advantages over the 90 nm technology family. This application note describes these advantages and provides guidelines to migrate from 90 nm to 65 nm devices.

Table 1. Features of 65 nm and 90 nm QDR Devices

| The following table high | lights the feat | ures and differences |

|--------------------------|-----------------|----------------------|

| between the 65 nm and 9  | 00 nm QDR de    | vice families.       |

|                                                      |                                                                                                                                        |                            | QDR II                                                                                            | DDRII   | DDRII<br>SIO | QDRII+  | QDRII+  | DDRII+  | DDRII+  | DDRII+<br>SIO | DDRII+<br>SIO |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------|---------|--------------|---------|---------|---------|---------|---------------|---------------|

| Read Latency- 90 nm and 65 nm                        |                                                                                                                                        | 1.5                        | 1.5                                                                                               | 1.5     | 2            | 2.5     | 2       | 2.5     | 2       | 2.5           |               |

| Write Latency-90 nm and 65 nm                        |                                                                                                                                        | 1                          | 1                                                                                                 | 1       | 1            | 1       | 1       | 1       | 1       | 1             |               |

| Frequency (Burst of 4)                               | 4 of 4\                                                                                                                                | 65 nm                      | 333 MHz                                                                                           | 333 MHz | N/A          | 450 MHz | 550 MHz | 450 MHz | 550 MHz | N/A           | N/A           |

| Frequency (Burst of 4)                               |                                                                                                                                        | 90 nm                      | 300 MHz                                                                                           | 300 MHz | N/A          | 400 MHz | 450 MHz | 400 MHz | 450 MHz | N/A           | N/A           |

| Frequency (Burst of 2)                               |                                                                                                                                        | 65 nm                      | 333 MHz                                                                                           | 333 MHz | 333 MHz      | 333 MHz | 333 MHz | 450 MHz | 550 MHz | 450 MHz       | 550 MHz       |

| Frequency (Burs                                      | 1012)                                                                                                                                  | 90 nm                      | 300 MHz                                                                                           | 300 MHz | 300 MHz      | 300 MHz | 300 MHz | 400 MHz | 450 MHz | 400 MHz       | 450 MHz       |

| Density 65 nm 90 nm                                  |                                                                                                                                        | 65 nm                      | 18Mb, 36Mb, 72Mb, & 144Mb                                                                         |         |              |         |         |         |         |               |               |

|                                                      |                                                                                                                                        | 90 nm                      | 18Mb, 36Mb, 72Mb                                                                                  |         |              |         |         |         |         |               |               |

| Organization (Bus Width) - 90 nm and 65 nm           |                                                                                                                                        | X9, X18, X36               |                                                                                                   |         |              |         |         |         |         |               |               |

| VDD (Core) - 90 nm and 65 nm                         |                                                                                                                                        | 1.8V +/-0.1V               |                                                                                                   |         |              |         |         |         |         |               |               |

| VDDQ (I/O) - 90 nm and 65 nm                         |                                                                                                                                        | 1.8V+/-0.1V or 1.5V+/-0.1V |                                                                                                   |         |              |         |         |         |         |               |               |

|                                                      | Logical Sing                                                                                                                           | le Bit Upset (LSBU) -65 nm | ) -65 nm 216 @ 85 degree celsius                                                                  |         |              |         |         |         |         |               |               |

| SER (FIT/Mb)                                         | Logical Sing                                                                                                                           | le Bit Upset (LSBU) -90 nm | 368 @ 85 degree celsius                                                                           |         |              |         |         |         |         |               |               |

| (Refer to <i>Note</i> ] Logical Mult and 65 nm       |                                                                                                                                        | Bit Upset (LMBU) -90 nm    | 0.01@ 85 degree celsius                                                                           |         |              |         |         |         |         |               |               |

| SEL (FIT/Dev) -90 nm and 65 nm                       |                                                                                                                                        | 0.1 @ 85 degree celsius    |                                                                                                   |         |              |         |         |         |         |               |               |

| Clock<br>generation                                  | eration Phase Locked Loop (PLL) -65 nm                                                                                                 |                            | Yes (PLL Lock time) :20us                                                                         |         |              |         |         |         |         |               |               |

| and Lock Time  Delay Locked Loop (DLL) -90 nm        |                                                                                                                                        |                            | Yes(DLL lock time): 1024 clock cycles for QDRII/DDRII and 2048 clock cycles for the QDRII+/DDRII+ |         |              |         |         |         |         |               |               |

| Input Clocks for Output Data (C,C#)90 nm and 65 nm   |                                                                                                                                        | Yes No                     |                                                                                                   |         |              |         |         |         |         |               |               |

| Echo Clocks (CQ, CQ#)                                |                                                                                                                                        | Yes                        |                                                                                                   |         |              |         |         |         |         |               |               |

| PKG90 nm and 65 nm                                   |                                                                                                                                        | 165 Ball FBGA              |                                                                                                   |         |              |         |         |         |         |               |               |

| QVLD90 nm and 65 nm                                  |                                                                                                                                        | No Yes                     |                                                                                                   |         |              |         |         |         |         |               |               |

| ODT Applicable in 65 nm only. Not supported in 90 nm |                                                                                                                                        | No Yes                     |                                                                                                   |         |              |         |         |         |         |               |               |

| Note: For mor                                        | Note: For more details refer to Application Note AN54908, Accelerated Neutron SER Testing and Calculation of Terrestrial Failure Rates |                            |                                                                                                   |         |              | tes     |         |         |         |               |               |

January 27, 2010 Document No. 001-58815 Rev. \*A

1

# Advantages of 65 nm Technology Devices

#### **Faster Operating Frequencies**

The 65 nm technology devices are capable of operating at higher operating frequencies of 550 MHz and total data rates up to 80 Gbps. This results in significant bandwidth improvement (~23%) over the 90 nm QDR family of devices, which can operate upto a maximum frequency of 450 MHz. This improvement in operating frequency satisfies the higher banwidth requirements in networking application.

#### **Lower Power Consumption**

The 65 nm technology QDR devices have lower power consumption than the equivalent 90 nm technology QDR devices. The power saving is  $\sim\!30\%$  at worst case condition.

#### **Improved Data Valid Window**

The data valid window for the outputs of 65 nm QDR devices is about 21% wider than the 90 nm QDR devices. This improvement is achieved using a low jitter clock generating PLL (Phase Locked Loop) as opposed to a DLL (Delay Locked Loop) in the 90 nm technology device. The PLL filters the incoming jitter and corrects any duty cycle distortion for the inputs. The improved data valid window helps achieve better timing margins for the 65 nm technology device.

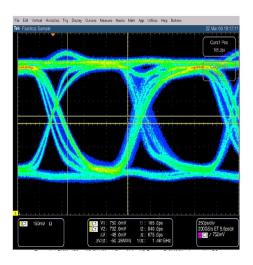

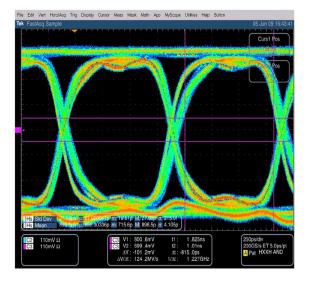

Figure 1 compares the data valid window of a 90 nm QDRII+ and a 65 nm QDRII+ device at 500 MHz. As shown in the figure, there is a significant improvement (~21%) in the data window for the 65nm QDRII+ devices.

Figure 1. Comparison of Data Valid Window

Ram 9 (90nm) QDRII+ DVW=675ps Worst Case Noise I/O Pattern @ 500MHz triggered by CQ

65nm QDRII+

DVW=815ps Worst Case Noise I/O Pattern @ 500MHz triggered by CQ

#### Improved Signal Integrity

The 65 nm technology QDRII+/DDRII+ devices have ondie termination for inputs such as data inputs, byte write signals, and input clocks (K/Kb). This feature is not present in the 90 nm technology QDRII+/DDRII+ devices. On-die termination eliminates the need for external termination resistors thereby reducing the cost and power consumed by external resistors. It also improves signal integrity, simplifies board routing, and reduces the board area. For more details on on-die termination, refer to application note AN42468, *On-Die Termination for QDRII+/DDRII+ SRAMs*.

#### **Lower Input and Output Capcitances**

Compared with the 90 nm predecessors, the 65 nm QDR family of SRAMs has lower input and output capacitance by 60 percent. This translates to lower return loss and therefore lower reflections or discontinuity at the inputs. A lower capacitance also results in lower AC power consumption at the input.

# Design Changes to Migrate from 90 nm to 65 nm Family

The 65 nm QDR family of devices provides higher speed path for most applications. You can implement certain design changes in your existing designs to enable seamless transition from 90 nm to 65 nm QDR devices.

#### **Board Changes**

For higher performance, the board should be designed to perform at speeds up to 550 MHz.

#### **Host Controller Changes**

Echo clocks need to be used to latch the read data. If the existing design uses a K or C clock for the read data capture, then the host controller design must be changed to use echo clocks because this yields better timing margins for higher frequencies.

The memory controller software should also be modified to accommodate the PLL lock time of 20 µs in the 65 nm technology device compared to the DLL lock time of 1024 clock cycles for the QDRII/DDRII and 2048 clock cycles for the QDRII+/DDRII+ devices in the 90 nm family.

#### **Pinout Changes**

In the QDRII device, the pins P6 and R6 are used as C and C# clocks. In the 90 nm technology QDRII+ devices, P6 is used as the QVLD pin and R6 is a NC (No connect).

In the 65 nm technology node, the QDRII+ devices are offered in two flavors: ODT enabled and ODT disabled devices. No change needs to be made when migrating from a 90 nm QDRII+ device to a 65 nm technology ODT disabled QDRII+ device as the pinouts are identical.

However, when migrating from a 90 nm technology QDRII+ device to a 65 nm technology ODT enabled device, the Ball R6 is an ODT pin instead of a NC (No Connect).

The ODT pin is used to select high range or low range of impedance for the inputs.

#### Summary

The 65 nm technology QDR family of devices provides the ability to achieve high performance and bandwidth with few changes to existing boards. It also has the capability to create new designs. This is possible by designing boards and host controllers to meet both support high performance of up to 550 MHz and 80 Gbps bandwidth in the next generations without any changes to the existing boards or host controllers.

[+] Feedback

3

### **Document History**

Document Title: Advantages of 65 nm Technology over 90 nm Technology QDR® Family of SRAMs

Document Number: 001-58815

| Revision | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                              |

|----------|---------|--------------------|--------------------|----------------------------------------------------|

| **       | 2847143 | NJY                | 01/13/10           | New application note                               |

| *A       | 2867379 | SHEA               | 01/27/10           | Minor ECN to correct document number in the footer |

QDR is a registered trademark of Cypress Semiconductor Corp. All other trademarks or registered trademarks referenced herein are the property of their respective owners.

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709 Phone: 408-943-2600 Fax: 408-943-4730 http://www.cypress.com/

© Cypress Semiconductor Corporation, 2010. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

This Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.