## Reference Schematic Design Recommendation for QDR®-DDR II/II+/Xtreme SRAMs – KBA84386

Question: Where can I get a recommended reference schematic design for QDR-DDR II/II+/Xtreme products?

**Answer:** This article provides reference schematics for QDR-DDR II/II+/Xtreme devices. You can use these schematics, which are derived from an internal characterization board, as examples for your designs. However, you must perform signal integrity simulations before doing so.

Refer to the application note <u>AN4065 - QDR™-II, QDR-II+, DDR-II, and DDR-II+ Design Guide</u> for different termination schemes, designs, and signal integrity guidelines. For more information on the QDR-DDR II/II+/Xtreme SRAMs, refer to the respective datasheets in the <u>Sync SRAM</u> category.

## Reference Schematic for QDR-DDR II/II+/Xtreme SRAMs (from internal characterization board)

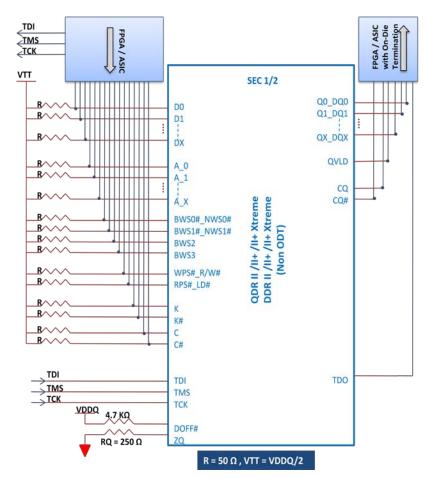

Figure 1. (a) QDRII/II+/II+Xtreme-DDRII/II+/II+Xtreme (Non ODT) Reference Schematic

TDI FPGA / ASIC with On-Die Termination FPGA / ASIC TMS **ETCK** SEC 1/2 Q0\_DQ0 DO Q1\_DQ1 D1 QX\_DQX VTT DX QVLD A 0 A\_1 CQ QDR II /II+ /II+ Xtreme DDR II /II+ /II+ Xtreme (ODT) CQ# A\_X BWS0#\_NWS0# BWS1#\_NWS1# BWS2 BWS3 WPS#\_R/W# RPS#\_LD# K# C C# ODT#  $\underset{\mathsf{TCK}}{\longrightarrow} \mathsf{TDI}$ TDO TDI TMS TCK **VDDQ** 4.7 ΚΩ DOFF# RQ = 175Ω ZQ  $R = 50 \Omega$ , VTT = VDDQ/2

Figure 1. (b) QDRII/II+/II+Xtreme-DDRII/II+/II+Xtreme (ODT) Reference Schematic

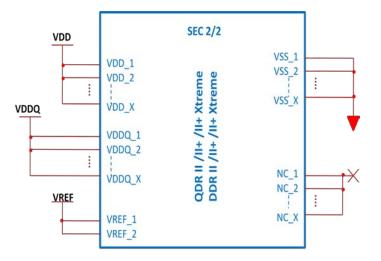

Figure 2. QDRII/II+/II+Xtreme-DDRII/II+/II+Xtreme (Supply Pins) Reference Schematic

## **Assumptions**

- The reference schematics provided in the previous section are from an internal characterization board. Cypress recommends that you perform signal integrity simulations with specific board conditions before finalizing your design.

- Figure 1 (a) and (b) are the reference schematics for all Non on-die termination (ODT) and ODT QDR-DDR II/II+/Xtreme SRAMs respectively. For example, if the part is an x18 device, then the data pin notation D<sub>[x:0]</sub> will be interpreted as D<sub>[17:0]</sub>.

- QDRII+/II+Xtreme-DDRII+/II+Xtreme devices do not have the input clocks C and C#.

- Non ODT QDRII+/II+Xtreme-DDRII/II+/II+Xtreme devices do not contain the ODT pin.

- ODT devices have an ODT feature for Data inputs (D<sub>[x:0]</sub>), Byte Write Selects (BWS<sub>[x:0]</sub>), and Input Clocks (K and K#). Hence, there is no termination for the D<sub>[x:0]</sub>, BWS<sub>[x:0]</sub>, K, and K# pins shown in Figure 1 (b). Refer to the application note <u>AN42468 On-Die</u>

<u>Termination for QDR™II+/DDRII+ SRAMs</u> that discusses the ODT scheme, implementation, advantages, and power calculation for the QDRII+ and DDRII+ family of Synchronous SRAMs on 65-nm technology devices.

- Data output (Q<sub>[x:0]</sub>) and Echo clock (CQ/CQ#) signals drive FPGA/ASIC without termination, considering the inputs of the FPGA/ASIC that supports ODT. In the case of FPGA/ASIC without ODT, Cypress recommends that you terminate (pull-up to V<sub>TT</sub>) Data output (Q<sub>[x:0]</sub>) and Echo clock (CQ/CQ#) signals to reduce signal integrity issues.

- The value of the termination resistor (R) is 50  $\Omega$ , because most designs have a trace characteristic impedance of 50  $\Omega$ . The termination resistor value must be equal to the characteristic impedance of the trace.

- An external resistor, RQ, must be connected between the ZQ pin on the SRAM and V<sub>SS</sub> to allow the SRAM to adjust its output driver impedance. The value of RQ must be five times the value of the intended line impedance driven by the SRAM. As a result, the value of RQ is 250 Ω to match the output impedance of 50 Ω in Figure 1 (a). The acceptable range of RQ that guarantees impedance matching with a tolerance of ±15% is between 175 Ω and 350 Ω, with V<sub>DDQ</sub> = 1.5V. The output impedance is adjusted every 1024 cycles upon power-up to account for drifts in supply voltage and temperature.

- The RQ is  $175\Omega$  in Figure 1 (b) considering the input impedance and ODT value of memory is  $50\Omega$ , ODT pin is LOW and output impedance is  $35\Omega$ . If the output impedance is  $50\Omega$  then it is recommended to use a  $15\Omega$  resistor in series with the output driver to match the trace impedance of  $50\Omega$ .

- Keep termination resistors as close to the device as possible to reduce the stub length, and thereby, reduce reflections.

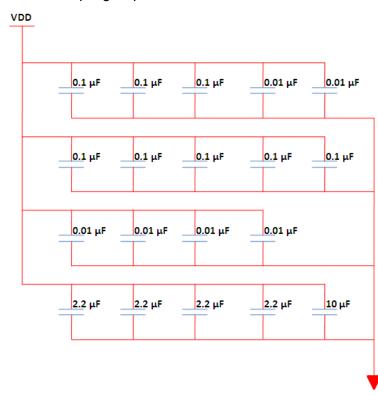

## **Decoupling Capacitor Recommendations for Power Supply Pins**

- Decoupling capacitors on power-supply pins play a significant role in filtering noise in the power supply.

- Cypress recommends that you place the decoupling capacitors close to the memory devices for best results.

- The following decoupling capacitor recommendations are from an internal characterization board:

Figure 3. Decoupling Capacitor Recommendation for V<sub>DD</sub>

Figure 4. Decoupling Capacitor Recommendation for  $V_{\text{DDQ}}$ VDDQ 0.01 μF 0.01 μF 0.01 μF 0.01 μF 0.01 μF 0.01 μF 0.1 μF 2.2 μF 2.2 μF 2.2 μF 2.2 μF 10 μF

**Note** Refer to the datasheets for  $V_{\text{DDQ}}$  value.

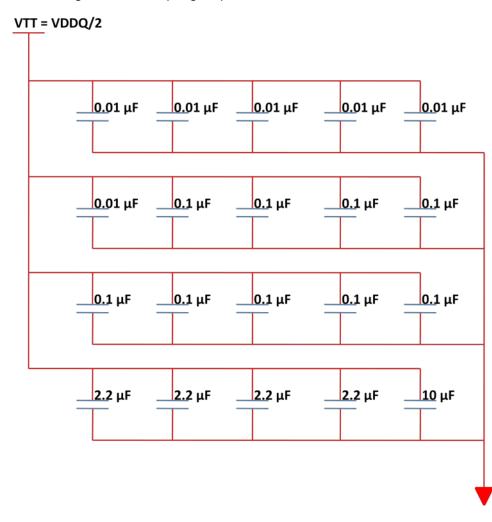

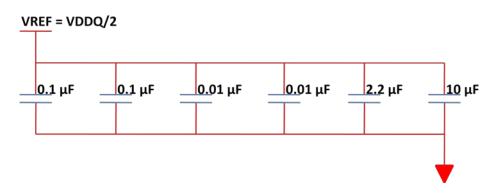

Figure 5. Decoupling Capacitor Recommendation for  $V_{TT}$

Figure 6. Decoupling Capacitor Recommendation for  $V_{\text{REF}}$

If you face any issue while creating your design or if you would like Cypress to do a schematic review, create a technical support case at <a href="https://www.cypress.com">www.cypress.com</a>.