# Interfacing PSoC® 1 to an SPI EEPROM

Project Name: PSoC1\_SPI\_EEPROM

Programming Language: C Software Version: PD5.2

Associated Part Families: CY8C29/27/24/22/21xxx, CY8C23x33, CY7C603xx

CY7C64215, CYWUSB6953, CY8CLED02/04/08/16,

CY8CLED04D01/02/03/04, CY8CTxx110, CY8CNP102

Related Hardware: CY3210 PSoC® Eval1 Board

Author: Madhan Kumar K

# **Objective**

This project interfaces PSoC1 to an Atmel SPI EEPROM (AT25080A) and performs write and read operations.

## Overview

A SPI communication is set up between PSoC and the SPI EEPROM (AT25080A) with the SPIM module in PSoC1 acting as the master and the EEPROM as the SPI slave. An array of 32 bytes is written to the EEPROM starting from location 0 to 31 and the same array is read back from the EEPROM.

## **User Module List and Placement**

The following table lists user modules used in this code example and the hardware resources occupied by each user module:

| User Module | Placement |

|-------------|-----------|

| LCD         |           |

| SPIM        | DCB02     |

# **User Module Parameter Settings**

The following table shows the user module parameter settings for the user modules used in the code example.

| SPIM           |                |                                                                                                                |  |

|----------------|----------------|----------------------------------------------------------------------------------------------------------------|--|

| Parameter      | Value          | Comments                                                                                                       |  |

| Clock          | VC2            | This sets VC2 as the clock source for the SPIM. It is set to 1.5 MHz (VC1/16) in the code example.             |  |

| MISO           | Row_0_Input_1  | MISO is connected to Row_0_Output_1 which is then connected to Serial Output pin of the EEPROM through P0 [1]. |  |

| MOSI           | Row_0_Output_0 | MOSI is connected to Row_0_Output_0 which is then connected to Serial Input of the EEPROM through P0 [0].      |  |

| SCLK           | Row_0_Output_2 | SCLK is connected to Clock input of EEPROM through Row_0_Output_2 and P0 [2].                                  |  |

| Interrupt Mode | -              | As polling mode is used in the firmware, this parameter is inconsequential.                                    |  |

| Clock Sync     | Sync to SysClk | Refer to the Clock Sync section of the SPIM data sheet.                                                        |  |

| Invert MISO    | Normal         | Implies we are not using the invert MISO option.                                                               |  |

#### **Notes**

- It is not necessary to use only VC2 as the clock source; it can be any of the clock sources as listed in the SPIM datasheet. Note that the maximum clock rate supported is 8.2 MHz for the SPIM module in PSoC.

- The actual bit rate of the SPIM is half the clock input. Hence, for a clock of 1.5 MHz, the clock rate from the SPIM is 750 KHz.

| LCD       |         |                                              |

|-----------|---------|----------------------------------------------|

| Parameter | Value   | Comments                                     |

| LCD port  | Port 2  | On the CY3210 boards, LCD is wired to Port 2 |

| BarGraph  | Disable | Not used in the code example                 |

# **Global Resources**

| Important Global Resources |       |                                         |

|----------------------------|-------|-----------------------------------------|

| Parameter                  | Value | Comments                                |

| VC2= VC1/N                 | 16    | Sysclk Divider, Divide VC1 Clock by 16. |

The other parameters can be retained at their default values or may be configured according to specific requirements.

## **Hardware Connections**

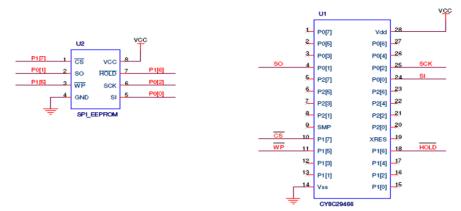

U2 is an 8 Kb (1024 X 8) EEPROM from Atmel. It is an 8-pin part with the following pin configuration:

| Pin Name | Function              |

|----------|-----------------------|

| CS       | Chip Select           |

| SCK      | Serial Data Clock     |

| SI       | Serial Data Input     |

| SO       | Serial Data Output    |

| GND      | Ground                |

| VCC      | Power Supply          |

| WP       | Write Protect         |

| HOLD     | Suspends Serial Input |

As shown in the following schematic, CS is connected to P1[7], SCK to P0[2], SI to P0[0], SO to P0[1], WP to P1[5], and Hold to P1[6]. WP and HOLD are made high in the firmware to enable write operation. The drive mode of pins used for WP, Hold, and Chip Select should be set to Strong.

The code example uses CY8C29466 PSoC1 microcontroller. This code example can be tested using the CY3210 Eval board.

# **Operation**

On reset, all hardware settings from the device configuration are loaded into the device and main.c is executed.

The following operations are performed by the firmware:

- The required variables are declared and initialized. After this, the data to be transmitted to the EEPROM is stored in the Tx\_Buf and the buffer to hold the data received from the EEPROM, Rx Buf is initialized to '0'.

- WP and HOLD pins are made high and Chip Select is made to '1', where WP is 'Write protect'.

- The Status Register of the EEPROM is written with a value of 0x00 to disable write protection to all the blocks.

- Data from TX\_Buf is written into the EEPROM inside the 'for' loop which iterates for 32 times. In each iteration, one byte of data is written from the buffer to the EEPROM. A 'for' loop of 32 iterations is used to write sequentially to EEPROM locations 0 to 31. For the sequence to be followed in the write operation, refer to the datasheet of AT25080A.

- After every write operation, wait for its completion by monitoring the RDY bit in the Status register.

- Data from the EEPROM is read back in Rx\_Buf using another for loop which also iterates for 32 times, reading one byte

of data for each iteration.

- The first 8 bytes of the Rx\_Buf are displayed on the LCD.

### **Testing the Project**

- Download the hex file 'PSoC1\_SPI\_EEPROM' to the CY8C29466 PSoC1.

- Make the connections between the EEPROM and CY8C29466 as shown in the Hardware Connections section.

- If you are using the CY3210, connect the LCD on the LCD jumper.

- On powering the board, the first line of the LCD should display '0001020304050607'.

PSoC is a registered trademark of Cypress Semiconductor Corp. PSoC Designer is a trademark of Cypress Semiconductor Corp. All other trademarks or registered trademarks referenced herein are the property of their respective owners.

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709 Phone: 408-943-2600 Fax: 408-943-4730 http://www.cypress.com/

© Cypress Semiconductor Corporation, 2009-2011. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

This Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.