### **About this document**

### **Scope and purpose**

AN211898 introduces the host processor interface (HPI) of the EZ-PD™ CCG3 and CCG4 devices. It describes the HPI architecture and register set, gives application examples, and explains how the embedded controller (EC) can update the CCG3/4 device's firmware over the host processor interface (HPI).

### **Table of contents**

| Abou   | ut this document                                   |    |

|--------|----------------------------------------------------|----|

| Table  | e of contents                                      | 1  |

| 1      | Introduction                                       | 4  |

| 1.1    | Target Applications with HPI                       |    |

| 1.2    | CCG3/4 Related Resources                           |    |

| 2      | HPI Specification                                  | 6  |

| 2.1    | HPI Protocol                                       | 6  |

| 2.1.1  | Command-Response Model                             | 6  |

| 2.1.2  | Asynchronous PD Message and Event Reporting        | 7  |

| 2.1.3  | Data Memory Read and Write Operations              | 11 |

| 2.2    | Power-Up Initialization Sequence for CCG3/4 and EC | 11 |

| 2.3    | HPI Physical Layer                                 | 13 |

| 2.4    | HPI Transport Layer                                | 14 |

| 2.4.1  | I <sup>2</sup> C Write to CCG3/4                   | 14 |

| 2.4.2  | l <sup>2</sup> C Read from CCG3/4                  | 15 |

| 2.4.3  | INTR# GPIO                                         | 15 |

| 2.5    | HPI Register Overview                              | 16 |

| 2.6    | HPI Differences between CCG1/2 and CCG3/4          | 17 |

| 3      | HPI Register Set                                   | 18 |

| 3.1    | Device Information Registers                       | 22 |

| 3.1.1  | DEVICE_MODE                                        | 22 |

| 3.1.2  | BOOT_MODE_REASON                                   | 23 |

| 3.1.3  |                                                    |    |

| 3.1.4  | BOOT_LOADER_LAST_ROW                               | 24 |

| 3.1.5  | INTR_REG                                           | 24 |

| 3.1.6  | <b>– –</b>                                         |    |

| 3.1.7  |                                                    |    |

| 3.1.8  | <u> </u>                                           |    |

| 3.1.9  | =                                                  |    |

| 3.1.10 |                                                    |    |

| 3.1.1  |                                                    |    |

| 3.1.12 | =                                                  |    |

| 3.1.13 |                                                    |    |

| 3.1.14 | <del>-</del>                                       |    |

| 3.1.15 | .5 SLEEP_CTRL                                      | 31 |

|        |                                                    |    |

### **Table of contents**

| 3.1.16  | BATTERY_STAT                                | 31 |

|---------|---------------------------------------------|----|

| 3.1.17  | Vendor-Specific Registers                   | 32 |

| 3.2     | PD Registers                                | 32 |

| 3.2.1   | Status Registers                            | 33 |

| 3.2.1.1 | TYPE_C_STATUS                               | 33 |

| 3.2.1.2 | PD_STATUS                                   | 34 |

| 3.2.1.3 | CURRENT_PDO                                 | 37 |

| 3.2.1.4 | CURRENT_RDO                                 | 37 |

| 3.2.1.5 | CURRENT_CABLE_VDO                           | 37 |

| 3.2.1.6 | EFFECTIVE_SOURCE_PDO_MASK                   | 38 |

| 3.2.1.7 | EFFECTIVE_SINK_PDO_MASK                     | 38 |

| 3.2.1.8 | PORT_INTR_STATUS                            | 39 |

| 3.2.2   | Control Registers                           | 40 |

| 3.2.2.1 | SWAP_RESPONSE                               | 40 |

| 3.2.2.2 | SELECT_SOURCE_PDO                           | 40 |

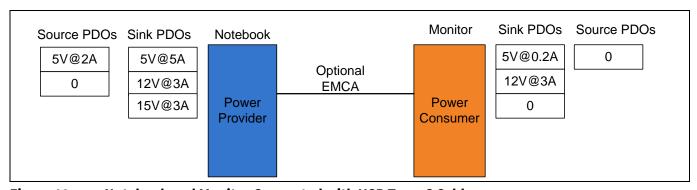

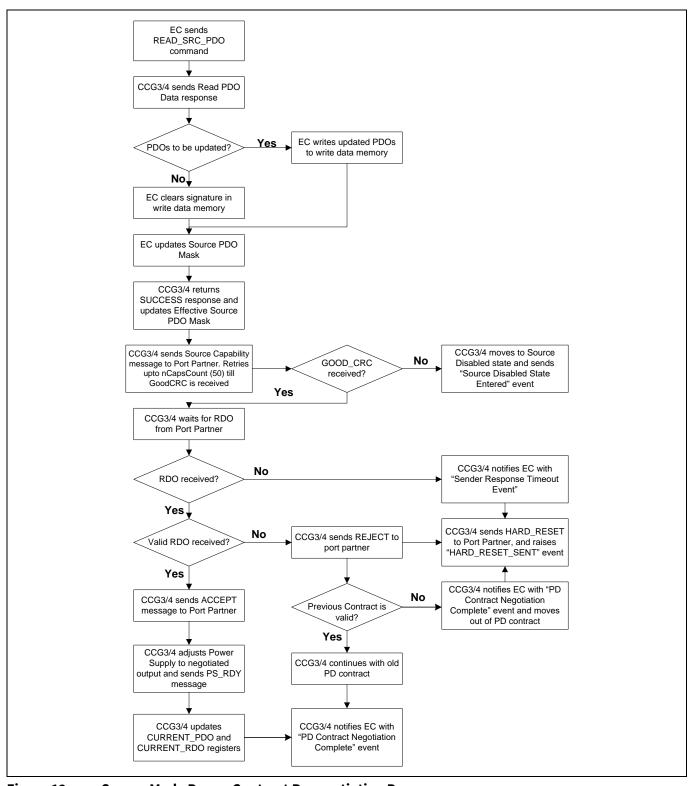

| 3.2.2.3 | Source Mode Power Renegotiation Flow        | 41 |

| 3.2.2.4 | SELECT_SINK_PDO                             | 44 |

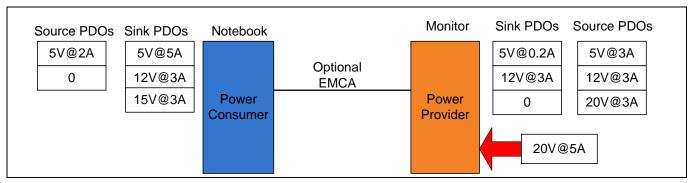

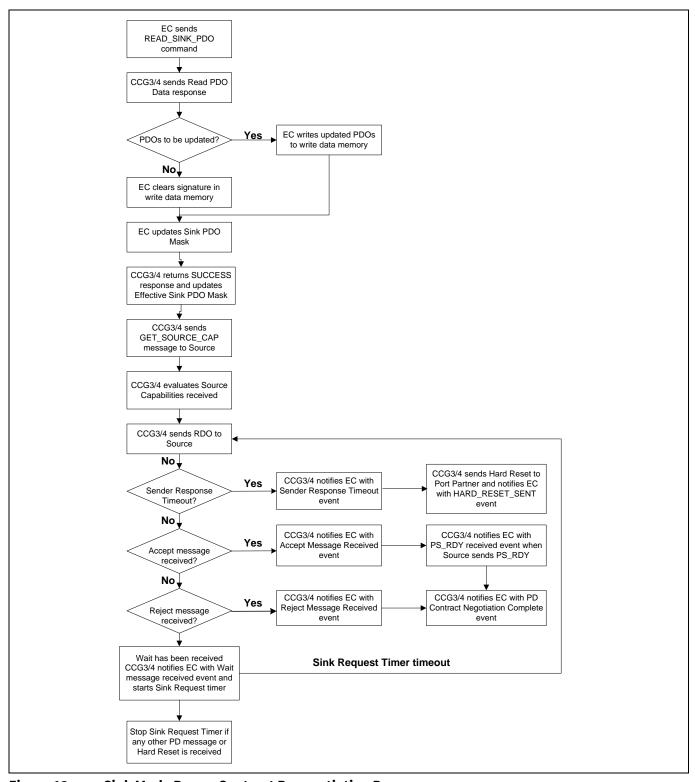

| 3.2.2.5 | Sink Mode Power Renegotiation Flow          | 45 |

| 3.2.2.6 | PD_CONTROL                                  | 46 |

| 3.2.2.7 | EVENT_MASK                                  | 48 |

| 3.2.2.8 | CMD_Timeout                                 | 50 |

| 3.2.3   | Events and Responses                        | 50 |

| 3.2.3.1 | RESPONSE_Register                           | 50 |

| 3.2.3.2 | CCG3/4 Response and Event Codes             |    |

| 3.2.4   | Summary                                     | 56 |

| 3.3     | VDM Registers                               | 57 |

| 3.3.1   | VDM_CONTROL                                 |    |

| 3.3.2   | VDM_EC_CONTROL                              | 58 |

| 3.4     | Alternate Mode (DisplayPort) Registers      |    |

| 3.4.1   | ALT_MODE_CMD                                | 59 |

| 3.4.2   | APP_HW_CMD                                  | 60 |

| 3.4.3   | ACTIVE_EC_MODES                             |    |

| 3.4.4   | Alternate Mode Events                       |    |

| 3.4.5   | Alternate Mode Hardware Events              |    |

| 3.4.6   | Summary                                     | 63 |

| 4 Ap    | plication Examples                          | 64 |

| 4.1     | CCG3/4 Firmware Update                      |    |

| 4.1.1   | CCG3/4 Device Firmware Update Approach      | 64 |

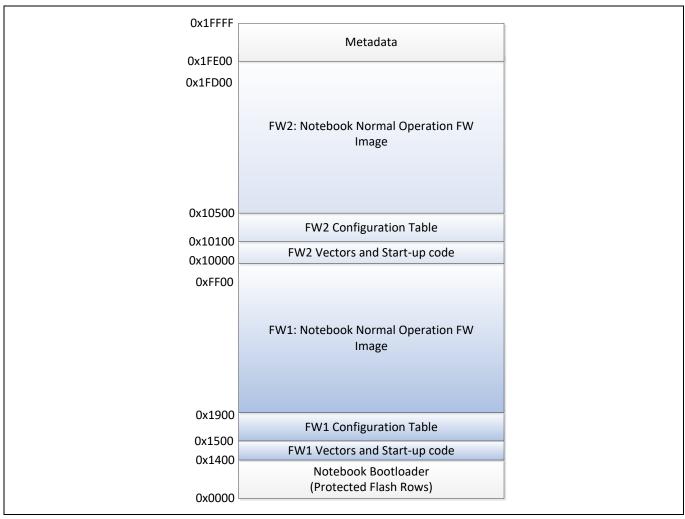

| 4.1.1.1 | Dual Firmware Mode                          | 64 |

| 4.1.2   | CCG3/4 Notebook Firmware Flash Map          |    |

| 4.1.2.1 | Dual Firmware Mode                          | 64 |

| 4.1.3   | Bootloader Registers                        | 66 |

| 4.1.3.1 | Status Registers                            | 66 |

| 4.1.3.2 | Command Registers                           | 66 |

| 4.1.4   | Firmware Update in Dual Firmware Mode       |    |

| 4.1.5   | Pseudo-Code to Update CCG3/4 Firmware by EC |    |

| 4.1.6   | Error Handling                              |    |

| 4.1.7   | Configuration Table Update Procedure        |    |

| 4.1.8   | Reading Firmware Version from .cyacd File   | 70 |

| 4 2     | Initialization of PD Commands over HPI      | 70 |

### **Table of contents**

| 4.2.1    | EC-CCG3/4 Initialization Sequence | 71 |

|----------|-----------------------------------|----|

| 4.2.2    |                                   | 78 |

| 4.2.3    |                                   | 78 |

| 4.2.4    |                                   | 78 |

| 4.2.5    | •                                 | 80 |

| 4.2.6    | ·                                 | 81 |

| 4.2.7    | Trigger VCONN Source Swap         | 82 |

| 4.2.8    |                                   | 82 |

| 4.2.9    |                                   | 83 |

| 4.2.10   | Send Hard Reset                   | 83 |

| 4.2.11   | Send Soft Reset                   | 83 |

| 4.2.12   | Send Cable Reset to EMCA          | 84 |

| 4.2.13   | Send Soft Reset to EMCA           | 84 |

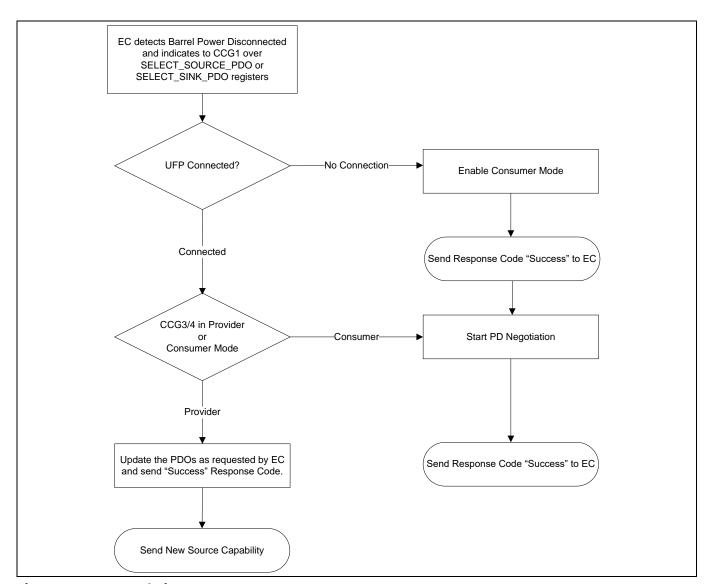

| 4.2.14   | Barrel Connect and Disconnect     | 85 |

| 4.2.14.1 | Barrel Connect                    | 85 |

| 4.2.14.2 | Barrel Disconnect                 | 86 |

| 4.2.15   | Updating Type-C Profile           | 86 |

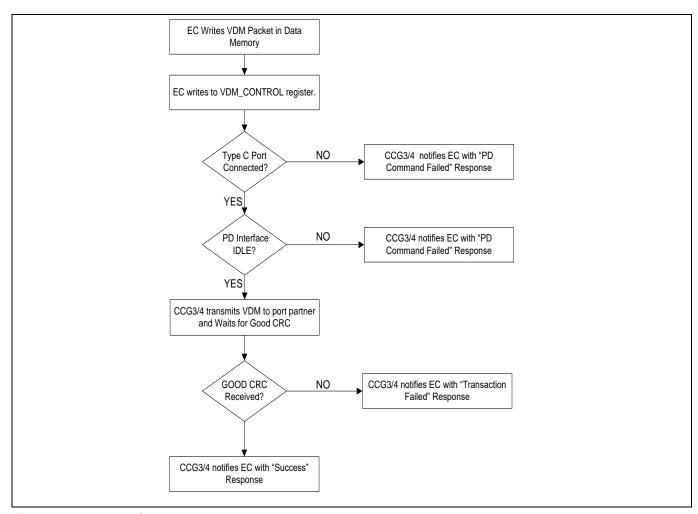

| 4.3      | VDM Handling and DisplayPort      | 87 |

| 4.3.1    | Sending VDMs to the Port Partner  | 87 |

| 4.3.2    | Response from Port Partner        | 87 |

| 4.3.3    | Unstructured VDMs                 | 89 |

| 4.3.4    | Alternate Mode Handling           | 89 |

| 4.3.4.1  | DisplayPort Alternate Mode        | 90 |

| 4.3.4.2  | DisplayPort Specific Events       | 90 |

| 4.3.4.3  | DisplayPort Specific Commands     | 90 |

| Revision | history                           | 92 |

|          |                                   |    |

Introduction

#### Introduction 1

USB Power Delivery (PD) Specification Revision 2.0 defines power delivery up to 100 W (20 V at 5 A) over existing USB standards. The USB Type-C Cable and Connector Specification details a new reversible and sub-3-mm slim connector design that supports 100 W of power along with USB and non-USB signals such as DisplayPort. CCG3 and CCG4 devices (referred to collectively as CCG3/4 in the remainder of this document) comply with the latest USB Type-C and PD standards and provide a complete USB Type-C and Power Delivery solution for notebooks, monitors, docking stations, power adapters, and other USB PD applications.

CCG3 is a single Type-C PD port device, whereas CCG4 supports dual Type-C PD ports. Refer to AN210403 -Hardware Design Guidelines for Dual Role Port Applications Using EZ-PD USB Type-C Controllers to learn about these Type-C PD controllers and the differences among them. See AN96527 - Designing USB Type-C Products Using Cypress's CCG1 Controllers for details on Type-C and power delivery channels.

CCG3/4 devices communicate with the attached Type-C PD device to manage the USB Type-C events and control the power delivery as defined in the USB Type-C and USB PD Specifications. For example, in a notebook system design, battery charging or discharging is managed by the battery charger controller (BCC) and embedded controller (EC) (also called the host processor). The EC communicates with the CCG3/4 device over the HPI to negotiate for power with the attached Type-C device based on the charge present in the battery of the notebook. The HPI is provided over a standard I<sup>2</sup>C interface such that an EC can monitor and control the run-time operation of the CCG3/4 device in any application.

This application note describes the HPI architecture and explains the HPI register set to kick-start the design. It explains how the HPI in the CCG3 and CCG4 devices provides capabilities to the EC in a system to read or change power profiles, monitor status, and update the CCG3 or CCG4 firmware. Various application examples of the HPI illustrate how CCG3/4 can communicate with the EC to read or change power profiles with an attached port partner. Also covered is communication of the CCG3/4 device with the EC to control the alternate mode, such as DisplayPort, as well as reconfiguration of display mux controllers.

#### 1.1 **Target Applications with HPI**

The HPI of a CCG3/4 device can be used in applications where the embedded controller needs to communicate with the CCG3/4 device for power negotiations or firmware update. Typical applications of HPI are listed as below:

- **Notebooks**

- **Docking stations**

- Monitors

- Dongles

#### 1.2 **CCG3/4 Related Resources**

The CCG4 design resources include datasheets, application notes, evaluation kits, reference designs, and firmware development and debugging tools. **Table 1** summarizes the resources.

Table 1 **CCG3/4 Related Resources**

| Category  | Available Resources                          | Where to Find Resources |

|-----------|----------------------------------------------|-------------------------|

| Datasheet | CCG3 datasheet                               | CCG3 Datasheet          |

|           | CCG4 datasheet                               | CCG4 Datasheet          |

| Hardware  | Evaluation kit – schematic, board files, and | CY4531 CCG3 EVK         |

|           | documentation                                | CY4541 CCG4 EVK         |

### Introduction

| Category                               | Available Resources                                                                                                          | Where to Find Resources                     |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| Application<br>Notes                   | Hardware design guidelines including recommendations for resistors, decoupling capacitors for power supplies, and PCB layout | AN210403                                    |

|                                        | Getting started with CCG4                                                                                                    | AN210771                                    |

|                                        | Designing USB Type-C products using the CCG1 controllers                                                                     | AN96527                                     |

| Programming<br>Specifications<br>Guide | The programming reference manual gives information necessary to program the nonvolatile memory of the CYPD4xxx devices       | Programming Specifications<br>Guide         |

| Host PC<br>Software                    | Software Development Kit                                                                                                     | EZ-PD CCGx SDK                              |

| Software                               | GUI-based Windows application to help users configure the CCG4 controller                                                    | EZ-PD Configuration Utility                 |

|                                        | Firmware development tool                                                                                                    | PSoC Creator 3.3 SP1 or later               |

|                                        | Firmware programming tool                                                                                                    | PSoC Programmer 3.24 or later               |

| Debugging<br>Tools                     | CY4500 EZ-PD Analyzer schematic, board files, documentation, and the EZ-PD Analyzer Tool                                     | CY4500 EZ-PD Analyzer                       |

| Other<br>Collateral                    | Knowledge base articles                                                                                                      | Knowledge Base Articles for CCG4 Controller |

**HPI Specification**

# 2 HPI Specification

This specification describes the HPI protocol used in CCG3/4. It includes a description of the HPI physical and transport layer, initialization sequence, and HPI registers.

### 2.1 HPI Protocol

This section documents the high-level protocol of the CCG3/4 device's HPI.

### 2.1.1 Command-Response Model

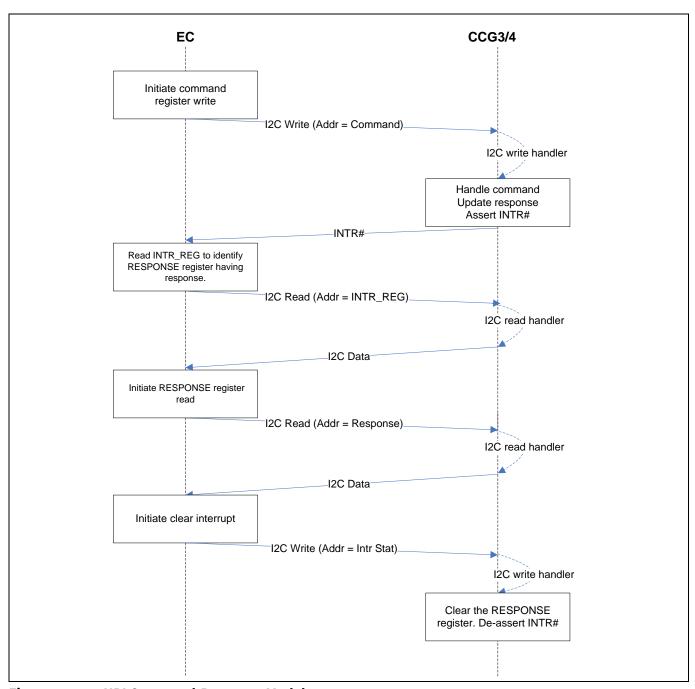

**Figure 1** shows the HPI command-response model between the EC and CCG3/4. The EC sends commands to CCG3/4 by writing to the command registers. The CCG3/4 device sends command responses to the EC through Response registers maintained in the HPI space. The responses for device commands and USB PD commands for each Type-C port are reported through separate registers. The RESPONSE\_REGISTER is used only to provide responses associated with device commands. The PD\_RESPONSE registers corresponding to each USB PD port are used to provide responses associated with PD commands.

CCG3/4 uses the INTR# pin to notify the EC that a response is available in a register. The EC needs to read the interrupt register (INTR\_REG) to identify the RESPONSE register that has the response. EC reads only that particular RESPONSE register. Subsequently, the EC reads the response and then clears the interrupt by writing to the Interrupt Status register (INTR\_REG). INTR\_REG contains separate status bits for each Response register. The EC is expected to read the RESPONSE register and clear the interrupt status before sending a new command (register write). The CCG3/4 device clears the contents of the RESPONSE register only after the EC writes to INTR\_REG. If the EC sends a new command before reading an outstanding response to a previous command, the response to the new command is queued in the internal message queue. The INTR# pin will be asserted if at least one of the RESPONSE registers contains a message. The CCG3/4 device de-asserts the INTR# pin when the interrupt status has been cleared.

Note:

The rest of this document uses the term "RESPONSE register" to refer to both the RESPONSE\_REGISTER and the PD\_RESPONSE register for simplicity, unless a specific reference is required. The RESPONSE\_REGISTER is used only for operations related to firmware update and switch firmware mode. Responses and events related to PD operation are sent through the PD\_RESPONSE register.

**HPI Specification**

Figure 1 **HPI Command-Response Model**

#### 2.1.2 **Asynchronous PD Message and Event Reporting**

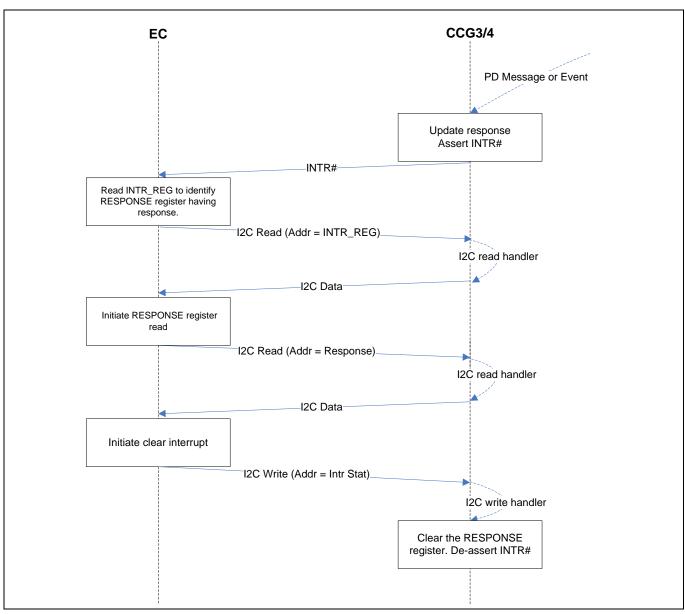

In addition to issuing responses to commands received, the PD\_RESPONSE registers are also used by CCG3/4 to notify the EC about asynchronous PD messages and device events. Figure 2 shows the asynchronous PD message and event reporting mechanism between the EC and CCG3/4 over the HPI. CCG3/4 will assert the INTR# pin when a new response or event is stored in the RESPONSE register. The EC is expected to clear the interrupt after reading the response/event from the registers.

**HPI Specification**

Figure 2 **Asynchronous PD Message and Event Reporting**

Asynchronous PD message and event reporting in CCG3/4 device application firmware mode: CCG3/4 notifies the EC about any state changes or command exchanges (such as Type-C port connect/disconnect detected) happening on the USB-PD interface through asynchronous events. Table 2 shows the various event codes used by CCG3/4 to communicate updates to the EC.

Table 2 **Events and Asynchronous Message Codes**

| Message Code(1<br>Byte) | Description                                                                                                                                                                                |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device-Specific Eve     | nts                                                                                                                                                                                        |

| 0x80                    | Reset Complete. Device underwent a reset and is back in operation mode. CCG uses this event as an indication to EC that CCG is ready to receive commands after initialization is complete. |

| 0x81                    | Message Queue Overflow. Message queue overflow detected.                                                                                                                                   |

# **HPI Specification**

| Message Code(1<br>Byte) | Description                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Type-C Specific Eve     | ents                                                                                                                                                                                                                                                                                                                                                                  |

| 0x82                    | Over Current Detected.                                                                                                                                                                                                                                                                                                                                                |

| 0x83                    | Over Voltage Detected.                                                                                                                                                                                                                                                                                                                                                |

| 0x84                    | Type C Port Connect Detected.                                                                                                                                                                                                                                                                                                                                         |

| 0x85                    | Type C Port Disconnect Detected.                                                                                                                                                                                                                                                                                                                                      |

| PD Control Message      | es and Contract-Specific Events                                                                                                                                                                                                                                                                                                                                       |

| 0x86                    | PD Contract Negotiation Complete.                                                                                                                                                                                                                                                                                                                                     |

| 0x87                    | SWAP Complete. EC is expected to start moving to new power requirements in sink mode within tSnkNewPower(max) – 15 ms and should complete within tSrcTransition(min) – 25 ms.                                                                                                                                                                                         |

| 0x88-0x89               | Reserved                                                                                                                                                                                                                                                                                                                                                              |

| A8x0                    | PS_RDY Message Received. EC is expected to meet new power requirements in sink mode within 15 ms.                                                                                                                                                                                                                                                                     |

| 0x8B                    | GotoMin Message Received. On receiving a GotoMin Message, the EC is expected to reduce its power consumption to the previously agreed minimum value within tSnkNewPower(max) – 15 ms. The EC should initiate contract renegotiation for returning to previous current level. The GotoMin request is valid until the next contract re-negotiation or disconnect event. |

| 0x8C                    | Accept Message Received.                                                                                                                                                                                                                                                                                                                                              |

| 0x8D                    | Reject Message Received.                                                                                                                                                                                                                                                                                                                                              |

| 0x8E                    | Wait Message Received.                                                                                                                                                                                                                                                                                                                                                |

| 0x8F                    | Hard Reset Received.                                                                                                                                                                                                                                                                                                                                                  |

| PD Data Message-S       | pecific Events                                                                                                                                                                                                                                                                                                                                                        |

| 0x90                    | VDM Received. This event indicates that CCG received a VDM from Port Partner. See section <b>4.3.2</b> . When acting as a UFP, the response VDM should be sent back within tVDMSenderResponse(max) specified by the USBPD specification. To support all command handling, the request should be responded to within 25 ms.                                            |

| Capability Message      | -Specific Events                                                                                                                                                                                                                                                                                                                                                      |

| 0x91                    | Source Capabilities Message Received.                                                                                                                                                                                                                                                                                                                                 |

| 0x92                    | Sink Capabilities Message Received.                                                                                                                                                                                                                                                                                                                                   |

| Resets and Error Sc     | renario Events                                                                                                                                                                                                                                                                                                                                                        |

| 0x9A                    | Hard Reset Sent to Port Partner                                                                                                                                                                                                                                                                                                                                       |

|                         | This event is reported when CCG3/4 sends HARD_RESET to port partner.                                                                                                                                                                                                                                                                                                  |

| 0x9B                    | Soft Reset Sent to Port Partner                                                                                                                                                                                                                                                                                                                                       |

|                         | Section <b>4.2.11</b>                                                                                                                                                                                                                                                                                                                                                 |

| 0x9C                    | Cable Reset Sent to EMCA                                                                                                                                                                                                                                                                                                                                              |

|                         | Section <b>4.2.12</b>                                                                                                                                                                                                                                                                                                                                                 |

| 0xA0                    | Unexpected Voltage on VBUS                                                                                                                                                                                                                                                                                                                                            |

|                         | CCG3/4 notifies EC with this event if CCG3/4 is DFP and unexpected voltage is detected on VBUS before CCG3/4 turns on VBUS. CCG3/4 does not continue with TYPE C Connect tasks in this case and does not start PD tasks. CCG3/4 stays in this state until a TYPE C disconnect. EC can choose to disable the TYPE C interface of CCG3/4 using the                      |

### **HPI Specification**

| Message Code(1<br>Byte) | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | PORT_DISBALE command in the PD_CONTROL register or notify the user to disconnect the port partner from the TYPE C connector.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0xA1                    | Type C Error Recovery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                         | CCG3/4 notifies EC with this event when CCG3/4 executes TYPE C ERROR Recovery.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0xA2-0xA5               | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Miscellaneous Ever      | nts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0xAA                    | Rp Change Detected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                         | CCG notifies EC with this event when CCG3/4 detects a change in the TYPE C "Rp" resistor value in Sink Mode. Note that Type C Source uses the Rp resistor to advertise the TYPE C Current level if PD Connection does not exist between the Port Partners. After a TYPE C Connection is established, CCG3/4 monitors the CC Voltage to determine the Rp resistor value. If Rp changes and PD Contract does not exist, CCG3/4 notifies EC with this event. The TYPE C status register's TYPE C Current field holds the present Rp value. EC is expected to adjust the current consumption over the TYPE C Interface accordingly. The current adjustment should be done within tSinkAdj(max) - tPDDebounce(max) = 60 ms - 20 ms = 40 ms. |

| Alternate-Mode-Re       | lated Events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0xB0                    | Alternate Mode event This event is sent for notification of Alternate mode-specific conditions like Alternate mode discovery, mode entry, and mode exit. The Event data specifies the SVID corresponding to the alt. mode, the event type, and any event-specific data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0xB1                    | Alternate Mode Hardware event                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                         | This event is sent for notification of the Alternate mode control hardware (MUX, HPD signal, etc.) state changes. The event data specifies all of the information related to the event.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

These events need to be enabled through explicit event mask updates performed at start-up time by the EC. CCG3/4 maintains internal queues to store these outstanding events, responses, and PD messages if the EC has not completed the read of the current message in the RESPONSE register. Separate queues are maintained for each USB PD port as well as for device-specific commands and events. Note that there is only one INTR# signal, which gets asserted when any Type-C or PD activity is detected on either of the Type-C ports. EC reads the RESPONSE register over HPI for both the Type-C ports as shown in Figure 5. CCG3/4 does not de-assert INTR#, even after the EC writes to INTR\_REG, if more events or messages are available in the internal queue. The EC must read out all the queued events and messages before sending a new command. It should always check the status of INTR# before sending a new command. The depth of the message queue is 8 events/responses per port. If the message queue overflows, CCG3/4 drops the last queued message and replaces it with a Message Queue Overflow event.

Asynchronous PD message and event reporting in boot mode: The CCG3/4 device does not maintain event queues in boot mode. It also does not support Type-C and PD functionality in boot mode. If the EC sends a new command before reading the response of a previous command, the CCG3/4 bootloader overwrites the RESPONSE register with the new response code and asserts INTR# pin to notify the EC that a response is available in a register.

In certain situations, CCG3/4 may not be able to handle the EC's command, for example, if a command is received from the EC when the CCG3/4 device is busy handling PD transactions on the Type-C interface.

### **HPI Specification**

CCG3/4 device responds with a PD Command Failed response status, and the EC may retry the command in following situations:

- If EC requests to transmit a PD control/data message when the Type-C port is not connected or does not exist.

- If EC issues a PD policy command when CCG3/4 is actively communicating on the Type-C interface.

- If CCG3/4 is not in PD Source/Sink Ready states as defined by USB Power Delivery (PD) Specification Revision 2.0.

### 2.1.3 Data Memory Read and Write Operations

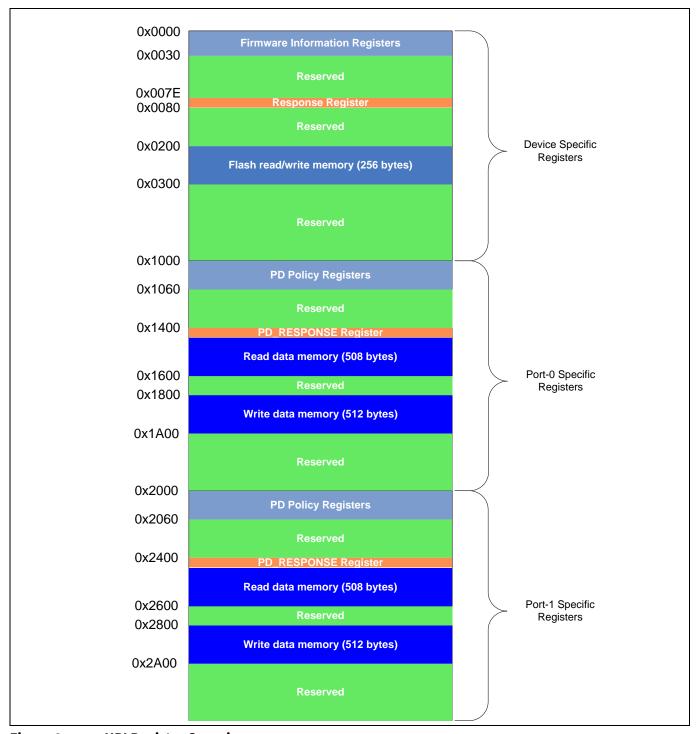

The CCG3/4 HPI implementation supports separate data memory regions for device-specific USB PD PORT\_0, and USB PD PORT\_1 (applicable only to CCG4) communication. All data memories are divided into two regions: The upper 512 bytes are write only, and the lower 512 bytes are read only (which includes 508 bytes read data memory and 4 bytes PD\_RESPONSE register) as shown in **Figure 8**.

CCG3/4 collects data written by the EC in an 8-byte-deep RX FIFO (internal hardware FIFO). It uses FIFO interrupts to determine the availability of data. CCG3/4 treats the first 2 bytes of the transaction as register address and the subsequent data bytes as register data. It collects data from the RX FIFO and keeps track of the internal write pointer. If the write pointer crosses the 128 or 256 byte boundary (as each flash memory row of CCG3 is 128 bytes and CCG4 is 256 bytes), CCG3/4 treats the write operation as invalid and drops the data bytes written by the EC.

CCG3/4 uses an I<sup>2</sup>C NACK mechanism to indicate error conditions to the EC. CCG3/4 may not be able to NACK the very first byte that crosses the 128-/256-byte boundary because it may be busy with other Type-C and PD interface interrupts such as Type-C attach or detach, initiation of power role swap or data role swap etc. Since RX FIFO is 8 bytes deep, one of the first 8 bytes that crosses the 128-/256-byte boundary is NACKed by CCG3/4.

Any data memory access operation (valid or invalid) does not result in response or event generation. If a read operation crosses the data memory boundary, the read pointer wraps around to offset 0. If a write operation crosses the data memory boundary, CCG3/4 drops further data bytes written by the EC. No action is taken if the write transaction fails or data memory does not get updated.

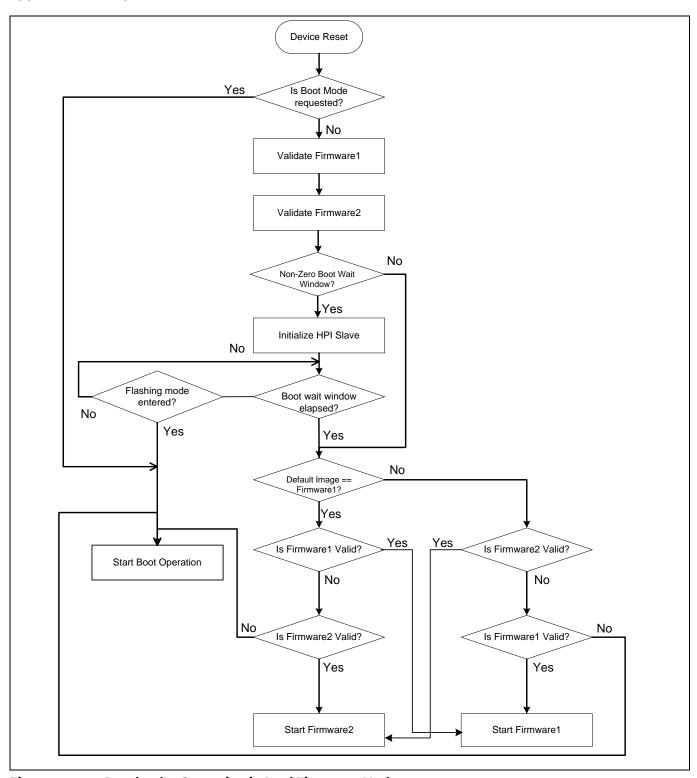

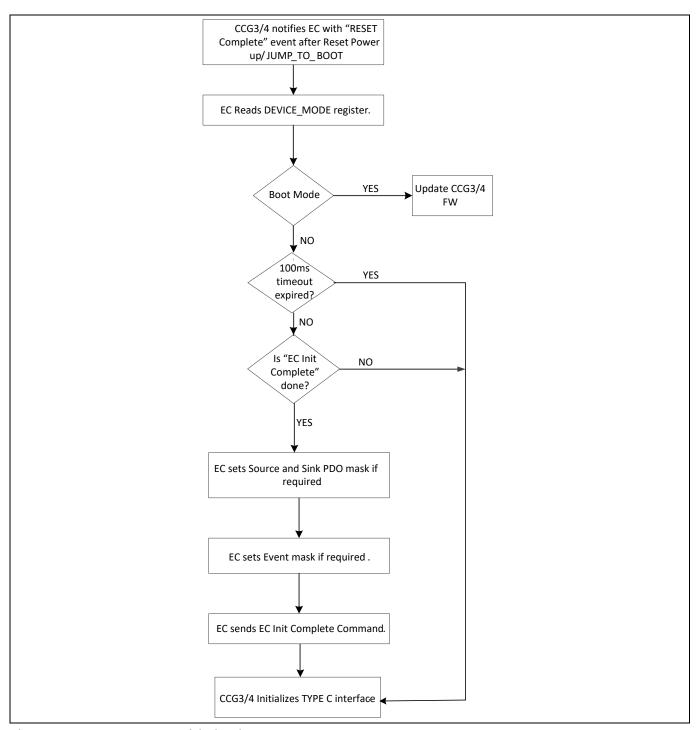

# 2.2 Power-Up Initialization Sequence for CCG3/4 and EC

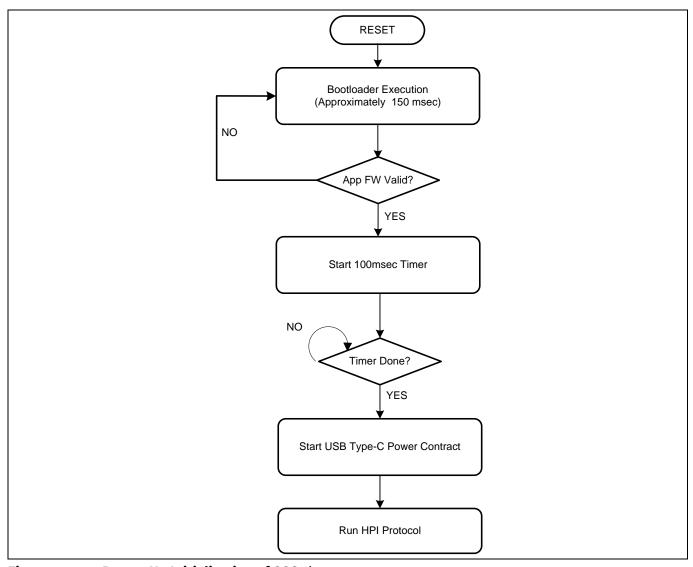

After a power up, CCG3/4 will go through the bootloader and will execute the application firmware upon successful validation of the firmware image. The bootloader execution takes approximately 150 msec. **Figure 3** shows the CCG3/4 power-up initialization sequence. After the application is launched, a 100-msec timer is enabled to allow the EC to change the settings of the CCG3/4 device before establishing the USB Type-C power contract.

**HPI Specification**

Power-Up Initialization of CCG3/4 Figure 3

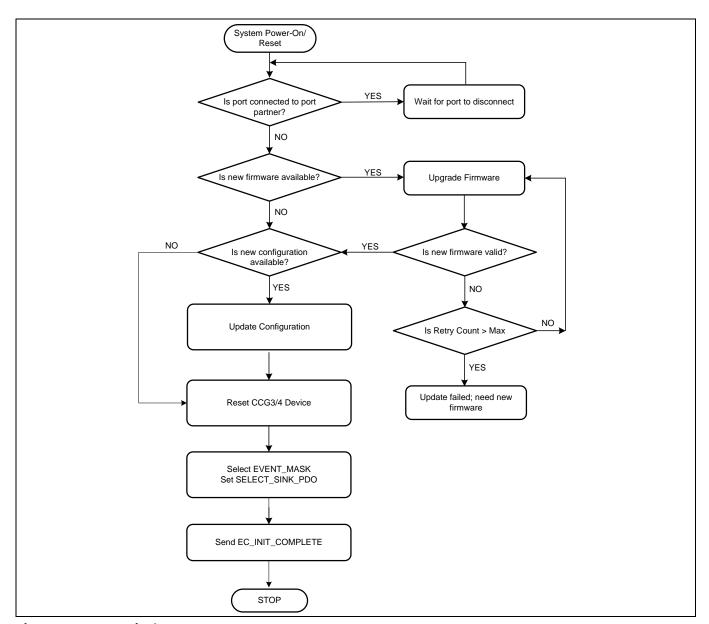

After the EC powers up, it may optionally initialize CCG3/4 and update its firmware, if required. The firmware update procedure for the CCG3/4 device is explained in section 4.1. The EC uses the EVENT\_MASK register to choose the events notified by the CCG3/4 device. By default, CCG3/4 handles all events and asynchronous PD messages autonomously and does not notify the EC. Depending on the mask value in this register, the EC can choose which events and messages will be notified. The EC uses the SELECT\_SINK\_PDO register to select sink mode PDOs at run time when the CCG3/4 device is configured as a power consumer or sink device. A typical EC boot-up sequence is shown in Figure 4.

### **HPI Specification**

Figure 4 **Typical EC Boot-Up Sequence**

#### 2.3 **HPI Physical Layer**

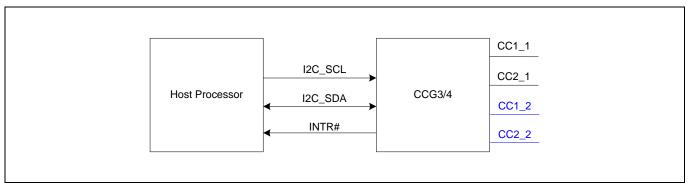

The physical connection to the EC is an I<sup>2</sup>C interface with an additional interrupt line (INTR#, active low signal), as shown in Figure 5. The CCG3/4 device will pull the INTR# pin low when it requires attention. CCG3/4 implements the HPI as an I<sup>2</sup>C slave interface (supported clock frequencies are 1 MHz, 400 kHz, and 100 kHz) and requires that the EC's I<sup>2</sup>C master support clock stretching. The CCG3/4 device has a 12-KB register space, which can be accessed over the I<sup>2</sup>C interface using a 2-byte register address.

The CCG3/4 device's I<sup>2</sup>C slave address (7 bit) can be set to one of three addresses depending on the bias set on the SWD\_CLK pin of the CCG3/4 device after reset. The CCG3/4 device uses the state of SWD\_CLK IO to configure the I<sup>2</sup>C slave address, which should be held stable at the desired value for a minimum of 200 ms (This 200ms time window includes the boot wait window of 100 ms and time taken to validate the application firmware image) whenever the CCG3/4 device goes through reset or performs a jump to bootloader/firmware operation. **Table 3** shows the HPI slave address selection options. If more than three CCG3/4 device addresses are needed, contact ccg@cypress.com to obtain customized firmware.

### **HPI Specification**

Figure 5 HPI Implemented as I<sup>2</sup>C Slave Interface

Table 3 Selecting the CCG3/4 I<sup>2</sup>C Slave Address

| SWD_CLK            | Slave Address |

|--------------------|---------------|

| Floating           | 0x08          |

| Pulled Low (1 kΩ)  | 0x40          |

| Pulled High (1 kΩ) | 0x42          |

Note:

The CC1\_2 and CC2\_2 lines correspond to the second PD port, which is currently available only on CCG4. Pin#15 of the CCG4 device is a fixed-function I/O, which is configured as an  $I^2C$  interrupt pin. While any CCG3 device's GPIO can be configured as an I<sup>2</sup>C interrupt pin, care should be taken to ensure that the application firmware and bootloader utilize the same GPIO as an interrupt pin.

#### 2.4 **HPI Transport Layer**

This section explains I<sup>2</sup>C bus communication and INTR# GPIO-specific details for the CCG3/4 register space's read and write operations. CCG3/4 supports the following read and write operations.

#### 2.4.1 I<sup>2</sup>C Write to CCG3/4

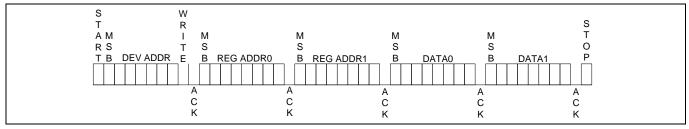

Figure 6 shows the I<sup>2</sup>C transfer sequence for a 2-byte write operation from the CCG3/4 device.

The first 2 bytes following a write preamble (device address) are the start address of the register write. The LS byte of the address is transferred first, followed by the MS byte. All bytes following the address bytes are the register data. CCG3/4 receives data in a temporary buffer and updates the register space only after STOP signal is received. The register space is updated after validation that the fields that are write-enabled are updated.

Write restart is not supported. Writes across invalid address regions are not supported. If the EC updates more than one command register data in a single write, the first command is processed, and the rest of the commands are ignored. Partial and unaligned register writes are treated as errors, and CCG3/4 responds with the Invalid Command code.

### **HPI Specification**

Figure 6 I<sup>2</sup>C Write to CCG3/4

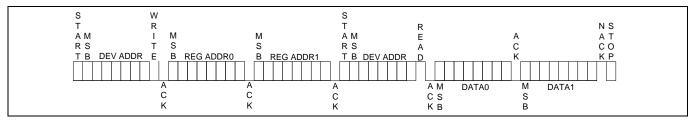

#### 2.4.2 I<sup>2</sup>C Read from CCG3/4

The EC uses this operation to read from the HPI register space. It has two phases:

- EC writes the register address followed by a restart on the bus instead of a stop.

- EC sends the read preamble and starts to read the data from the register space.

The maximum read size is 512 bytes. Reads beyond the valid address region will be NACKed by the CCG3/4 device. Figure 7 shows the I<sup>2</sup>C transfer sequence for a 2-byte read operation from the CCG3/4 device.

Figure 7 I<sup>2</sup>C Read from CCG3/4

The CCG3/4 device will NACK the read preamble if the EC does not write a register address followed by a restart before reading the register contents.

The I<sup>2</sup>C master on the EC must support clock stretching. The CCG3/4 device stretches the I<sup>2</sup>C clock in the following scenarios:

- At the ACK/NACK phase of the preamble: The preamble byte received from the EC is not automatically responded to with an ACK/NACK by the CCG3/4's hardware I<sup>2</sup>C block. The CCG3/4 device's firmware responds to the preamble byte received from the EC. If CCG3/4 is servicing Type-C and PD interrupts while the preamble is received, the clock is stretched until CCG3/4's firmware services the I<sup>2</sup>C request.

- The CCG3/4 device has an RX FIFO of 8 bytes to receive data transmitted by the EC. The clock is stretched at the ACK phase of the data byte if the RX FIFO is full and CCG3/4 cannot receive any more data. CCG3/4 stops the clock stretch and ACKs the next data byte when the CCG3/4 device reads the RX FIFO contents and the FIFO has space to receive subsequent data bytes.

#### 2.4.3 **INTR# GPIO**

INTR# GPIO is an active low signal. CCG3/4 drives INTR# GPIO low to notify the EC of responses, events, and asynchronous messages. The drive mode of INTR# GPIO is open drain. An external pull-up is required to detect INTR# GPIO assertion.

**HPI Specification**

#### **HPI Register Overview** 2.5

CCG3 supports one USB PD port whereas CCG4 supports two USB PD ports, which can be independently configured and used. A 2-byte addressed register space is used for CCG3/4 devices, so that the implementation allows for the addition of new registers and provides independent sets of registers to manage each USB PD port.

Figure 8 shows the HPI register space, which is divided into three sections as follows:

**HPI Register Overview** Figure 8

### **HPI Specification**

- Device-specific registers (0x0000-0x0FFF): This space contains all the command registers and status registers common to the CCG3/4 device (and unrelated to specific USB PD ports). It also contains the RESPONSE register, data memory, and flash read/write memory.

- Status registers: These registers provide information about the operating mode (such as firmware and bootloader) of the CCG3/4 device.

- Command registers: These registers are used to send device-level commands such as flash read/write to the CCG3/4 firmware.

- RESPONSE register: This space is used to respond to device-specific commands and to notify device-specific events to the EC.

- Flash read/write memory: This space is used as a buffer to read or write a complete flash row.

- Port-specific registers for PORT\_0 (0x1000-0x1FFF): This space contains all the command registers, status registers, and PD policy registers related to Type-C port 0. Only PORT\_0 will be available for single Type-C port devices such as CCG3 and the single Type-C port CCG4 (CYPD4125) device. It also contains a RESPONSE register similar to the device-specific registers and the data memory.

- Port-specific registers for PORT\_1 (0x2000-0x2FFF): This space is applicable only to the CCG4 device. These

registers are related to Type-C port 1 on the CCG4 device and have the same structure as the PORT\_0

registers.

Refer to HPI Register Set, for further details on the HPI register set.

### 2.6 HPI Differences between CCG1/2 and CCG3/4

Differences in the HPI implementation for CCG1/2 and CCG3/4 are as follows:

- CCG4 device has flash memory with 256-byte rows, requiring a 256-byte data memory region to do flash read/writes.

- CCG3/4 devices support additional features such as Thunderbolt mode that require additional PD configuration and status registers.

- CCG3/4 devices support a dual firmware application usage model, which requires additional registers to report firmware information.

- CCG4 device has two USB PD ports, which need to be independently managed through different sets of registers

- The configuration table is attached to the application firmware as a single firmware image file in CCG3/4 devices.

The changes in HPI definition are made in such a way that changes to the HPI implementation on the EC side are minimized. In summary, the changes made are:

- I<sup>2</sup>C addressing is 2 bytes instead of 1 byte. This change allows separate sets of registers for each USB-PD port and also provides scalability for future implementations with more than two ports.

- I<sup>2</sup>C addresses for each register are changed to implement a hierarchy based on the functionality of the registers. The addressing is done so as to make it easy for the EC to calculate the address for each PD port.

- New registers and fields are added in the device information registers to provide information about two firmware images.

- New PD configuration registers are added to support new firmware features (such as dynamic PDO update).

**HPI Register Set**

#### **HPI Register Set** 3

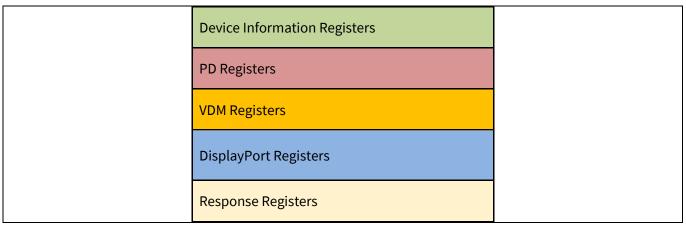

This section explains the CCG3/4 device's register set in detail. The HPI registers are listed in Table 4. They are categorized into device-specific registers and port-specific registers. Port-specific registers are further classified into PD registers, VDM registers, DisplayPort registers, and Response registers. The register set in Table 4 is color coded based on the different types, as shown in Figure 9.

Figure 9 **Types of HPI Registers**

Note that registers are 1 byte, 2 bytes, or 4 bytes in length, and one of them is 16 bytes in length. The byte order for multi-byte registers is little-endian.

Most of the registers are status registers that the EC can read to discover the current state of the CCG3/4 device. The CCG3/4 device updates these registers at run time. Control registers determine how the CCG3/4 device responds to certain events such as role swaps. Command registers are used by the EC to trigger changes such as source/sink PDO selection and VDM transmission. The EC and CCG3/4 use a command-response model, as explained in section 2.1.1. It is mandatory to read the response for a previous command prior to initiating the next command.

Table 4 **Definition of HPI Registers**

| Address | Name                 | Field          | Mode    | Access | Section |

|---------|----------------------|----------------|---------|--------|---------|

| 0x0000  | DEVICE_MODE          | Current mode   | BOOT/FW | R      | 3.1.1   |

| 0x0001  | BOOT_MODE_REASON     | Reason         | воот    | R      | 3.1.2   |

| 0x0002  | READ_SILICON_ID      | Silicon ID LSB | BOOT/FW | R      | 3.1.3   |

| 0x0003  | READ_SILICON_ID      | Silicon ID MSB | BOOT/FW | R      |         |

| 0x0004  | BOOT_LOADER_LAST_ROW | Last Row LSB   | воот    | R      | 3.1.4   |

| 0x0005  | BOOT_LOADER_LAST_ROW | Last Row MSB   | воот    | R      |         |

| 0x0006  | INTR_REG             | Interrupt      | BOOT/FW | R/W    | 3.1.5   |

| 0x0007  | JUMP_TO_BOOT         | Signature      | CTRL    | W      | 3.1.6   |

| 0x0008  | RESET                | Signature      | CTRL    | W      | 3.1.7   |

| 0x0009  | RESET                | Туре           | CTRL    | W      |         |

| 0x000A  | ENTER_FLASHING_MODE  | Signature      | воот    | W      | 3.1.8   |

| 0x000B  | VALIDATE_FW          | FW Mode        | воот    | W      | 3.1.9   |

| 0x000C  | FLASH_ROW_READ_WRITE | Signature      | воот    | W      | 3.1.10  |

| 0x000D  | FLASH_ROW_READ_WRITE | Command        | воот    | W      |         |

# **HPI Register Set**

| Address | Name                 | Field                                   | Mode    | Access | Section |

|---------|----------------------|-----------------------------------------|---------|--------|---------|

| 0x000E  | FLASH_ROW_READ_WRITE | Row Number LSB                          | воот    | W      |         |

| 0x000F  | FLASH_ROW_READ_WRITE | Row Number MSB                          | воот    | W      |         |

| 0x0010  | READ_ALL_VERSION     | BL Build Number<br>LSB                  | BOOT/FW | R      | 3.1.11  |

| 0x0011  | READ_ALL_VERSION     | BL Build Number<br>MSB                  | BOOT/FW | R      |         |

| 0x0012  | READ_ALL_VERSION     | BL Patch Version                        | BOOT/FW | R      |         |

| 0x0013  | READ_ALL_VERSION     | BL Version<br>Major(7:4)<br>Minor(3:0)  | BOOT/FW | R      |         |

| 0x0014  | READ_ALL_VERSION     | BL Application<br>Name LSB              | BOOT/FW | R      |         |

| 0x0015  | READ_ALL_VERSION     | BL Application<br>Name MSB              | BOOT/FW | R      |         |

| 0x0016  | READ_ALL_VERSION     | BL External Circuit<br>Specific Version | BOOT/FW | R      |         |

| 0x0017  | READ_ALL_VERSION     | BL Version<br>Major(7:4)<br>Minor(3:0)  | BOOT/FW | R      |         |

| 0x0018  | READ_ALL_VERSION     | FW Build Number<br>LSB                  | BOOT/FW | R      |         |

| 0x0019  | READ_ALL_VERSION     | FW Build Number<br>MSB                  | BOOT/FW | R      |         |

| 0x001A  | READ_ALL_VERSION     | FW Patch Version                        | BOOT/FW | R      |         |

| 0x001B  | READ_ALL_VERSION     | FW Version<br>Major(7:4) Minor<br>(3:0) | BOOT/FW | R      |         |

| 0x001C  | READ_ALL_VERSION     | FW Application<br>Name LSB              | BOOT/FW | R      |         |

| 0x001D  | READ_ALL_VERSION     | FW Application<br>Name MSB              | BOOT/FW | R      |         |

| 0x001E  | READ_ALL_VERSION     | FW External Circuit<br>Specific Version | BOOT/FW | R      |         |

| 0x001F  | READ_ALL_VERSION     | FW Version Major<br>(7:4) Minor (3:0)   | BOOT/FW | R      |         |

| 0x0020  | FW2_VERSION          | FW2_VERSION[0]                          | BOOT/FW | R      | 3.1.12  |

| 0x0021  | FW2_VERSION          | FW2_VERSION[1]                          | BOOT/FW | R      |         |

| 0x0022  | FW2_VERSION          | FW2_VERSION[2]                          | BOOT/FW | R      |         |

| 0x0023  | FW2_VERSION          | FW2_VERSION[3]                          | BOOT/FW | R      |         |

| 0x0024  | FW2_VERSION          | FW2_VERSION[4]                          | BOOT/FW | R      |         |

| 0x0025  | FW2_VERSION          | FW2_VERSION[5]                          | BOOT/FW | R      |         |

# **HPI Register Set**

| Address | Name                              | Field                                           | Mode    | Access | Section |

|---------|-----------------------------------|-------------------------------------------------|---------|--------|---------|

| 0x0026  | FW2_VERSION                       | FW2_VERSION[6]                                  | BOOT/FW | R      |         |

| 0x0027  | FW2_VERSION                       | FW2_VERSION[7]                                  | BOOT/FW | R      |         |

| 0x0028  | FIRMWARE_BINARY_LOCATION_REGISTER | FW1_START[0]                                    | BOOT/FW | R      | 3.1.13  |

| 0x0029  | FIRMWARE_BINARY_LOCATION_REGISTER | FW1_START[1]                                    | BOOT/FW | R      |         |

| 0x002A  | FIRMWARE_BINARY_LOCATION_REGISTER | FW2_START[0]                                    | BOOT/FW | R      |         |

| 0x002B  | FIRMWARE_BINARY_LOCATION_REGISTER | FW2_START[1]                                    | BOOT/FW | R      |         |

| 0x002C  | PDPORT_ENABLE                     | Enables or disables PD port                     | FW      | RW     | 3.1.14  |

| 0x002D  | SLEEP_CTRL                        | Controls Deep<br>Sleep mode                     | FW      | RW     | 3.1.15  |

| 0x002E  | BATTERY_STAT                      | Informs about dead battery conditions           | FW      | RW     | 3.1.16  |

| 0x0040  | VENDOR SPECIFIC                   | Vendor specific<br>register space (48<br>bytes) | FW      | RW     | 3.1.17  |

| 0x007E  | RESPONSE_REGISTER                 | Response/Message<br>Code                        | STATUS  | R      | 3.2.3.1 |

| 0x007F  | RESPONSE_REGISTER                 | Length                                          | STATUS  | R      |         |

| 0x1000  | VDM_CONTROL                       | VDM mode                                        | CMD     | W      | 3.3.1   |

| 0x1001  | VDM_CONTROL                       | Length                                          | CMD     | W      |         |

| 0x1002  | EFFECTIVE_SOURCE_PDO_MASK         | PDO Mask                                        | STATUS  | R      | 3.2.1.6 |

| 0x1003  | EFFECTIVE_SINK_PDO_MASK           | PDO Mask                                        | STATUS  | R      | 3.2.1.7 |

| 0x1004  | SELECT_SOURCE_PDO                 | Command                                         | CMD     | W      | 3.2.2.2 |

| 0x1005  | SELECT_SINK_PDO                   | Command                                         | CMD     | W      | 3.2.2.4 |

| 0x1006  | PD_CONTROL                        | Command                                         | CMD     | W      | 3.2.2.6 |

| 0x1008  | PD_STATUS                         | Status Bit Map<br>(b7:0)                        | STATUS  | R      | 3.2.1.2 |

| 0x1009  | PD_STATUS                         | Status Bit Map<br>(b15:8)                       | STATUS  | R      |         |

| 0x100A  | PD_STATUS                         | Status Bit Map<br>(b23:16)                      | STATUS  | R      |         |

| 0x100B  | PD_STATUS                         | Status Bit Map<br>(b31:24)                      | STATUS  | R      |         |

| 0x100C  | TYPE_C_STATUS                     | Status Bit Map                                  | STATUS  | R      | 3.2.1.1 |

| 0x1010  | CURRENT_PDO                       | PDO LSB                                         | STATUS  | R      | 3.2.1.3 |

| 0x1011  | CURRENT_PDO                       | PDO                                             | STATUS  | R      |         |

| 0x1012  | CURRENT_PDO                       | PDO                                             | STATUS  | R      |         |

| 0x1013  | CURRENT_PDO                       | PDO MSB                                         | STATUS  | R      |         |

| 0x1014  | CURRENT_RDO                       | RDO LSB                                         | STATUS  | R/W    | 3.2.1.4 |

| 0x1015  | CURRENT_RDO                       | RDO                                             | STATUS  | R/W    |         |

| 0x1016  | CURRENT_RDO                       | RDO                                             | STATUS  | R/W    |         |

# **HPI Register Set**

| Address | Name              | Field                                                       | Mode   | Access | Section |

|---------|-------------------|-------------------------------------------------------------|--------|--------|---------|

| 0x1017  | CURRENT_RDO       | RDO MSB                                                     | STATUS | R/W    |         |

| 0x1018  | CURRENT_CABLE_VDO | VDO LSB                                                     | STATUS | R      | 3.2.1.5 |

| 0x1019  | CURRENT_CABLE_VDO | VDO                                                         | STATUS | R      |         |

| 0x101A  | CURRENT_CABLE_VDO | VDO                                                         | STATUS | R      |         |

| 0x101B  | CURRENT_CABLE_VDO | VDO MSB                                                     | STATUS | R      |         |

| 0x101C  | ALT_MODE_CMD      | SVID[0]                                                     | CTRL   | R/W    | 3.4.1   |

| 0x101D  | ALT_MODE_CMD      | SVID[1]                                                     | CTRL   | R/W    |         |

| 0x101E  | ALT_MODE_CMD      | Alternate Mode ID                                           | CTRL   | R/W    |         |

| 0x101F  | ALT_MODE_CMD      | Alternate Mode<br>Data Role                                 | CTRL   | R/W    |         |

| 0x1020  | APP_HW_CMD        | CCG Data Role                                               | CTRL   | R/W    | 3.4.2   |

| 0x1021  | APP_HW_CMD        | Hardware Role                                               | CTRL   | R/W    |         |

| 0x1022  | APP_HW_CMD        | Command ID[0]                                               | CTRL   | R/W    |         |

| 0x1023  | APP_HW_CMD        | Command ID[1]                                               | CTRL   | R/W    |         |

| 0x1024  | EVENT_MASK        | Response Filter (b7:0)                                      | CTRL   | R/W    | 3.2.2.7 |

| 0x1025  | EVENT_MASK        | Response Filter<br>(b15:8)                                  | CTRL   | R/W    |         |

| 0x1026  | EVENT_MASK        | Response Filter<br>(b23:16)                                 | CTRL   | R/W    |         |

| 0x1027  | EVENT_MASK        | Response Filter<br>(b31:24)                                 | CTRL   | R/W    |         |

| 0x1028  | SWAP_RESPONSE     | Response<br>Override                                        | CMD    | R      | 3.2.2.1 |

| 0x1029  | ACTIVE_EC_MODES   | Used by EC to indicate if it is maintaining active EC modes | STATUS | R/W    | 3.4.3   |

| 0x102A  | VDM_EC_CONTROL    | Used by EC to indicate that it is ready to handle VDMs      | CTRL   | R/W    | 3.3.2   |

| 0x1030  | CMD_TIMEOUT       | Timeout periods for VDMs and PD commands                    | CTRL   | R/W    | 3.2.2.8 |

| 0x1031  | PORT_INTR_STATUS  | Reports the PD port status                                  | STATUS | R/W    | 3.2.1.8 |

| 0x1032  | PORT_INTR_STATUS  | Reports the PD port status                                  | STATUS | R/W    |         |

| 0x1033  | PORT_INTR_STATUS  | Reports the PD port status                                  | STATUS | R/W    |         |

| 0x1034  | PORT_INTR_STATUS  | Reports the PD port status                                  | STATUS | R/W    |         |

### **HPI Register Set**

| Address | Name        | Field      | Mode   | Access | Section |

|---------|-------------|------------|--------|--------|---------|

| 0x1400  | PD_RESPONSE | Reports PD | STATUS | R      |         |

|         |             | responses  |        |        |         |

| 0x1401  | PD_RESPONSE | Reports PD | STATUS | R      |         |

|         |             | responses  |        |        |         |

The following sections describe each register in detail. Rather than presenting them in numerical order, they use a logical order since several registers are linked and need an introduction to their category.

#### **Device Information Registers** 3.1

This section covers the system registers that can be read at any time.

#### 3.1.1 **DEVICE\_MODE**

This register indicates the active device mode, as described in **Table 5**. The CCG3/4 device can be either in bootloader or normal (application firmware) operation mode. The device is in boot mode only if the application firmware image is not valid or if the application requests the CCG3/4 device to jump to boot mode. This register is available for access in both the bootloader and normal firmware mode.

Table 5 **DEVICE\_MODE** Register

| DEVICE_MODE: 1 Byte       |

|---------------------------|

| CCG3/CCG4 Address: 0x0000 |

| Field   | Field Name | R/W | Description                                                                                                         |

|---------|------------|-----|---------------------------------------------------------------------------------------------------------------------|

| Byte[0] | Current    | R   | b7                                                                                                                  |

|         | mode.      |     | 0 – HPIv1 mode. Single-byte HPI addressing, only bootloader can do flash read/write.                                |

|         |            |     | 1 – HPIv2 mode. Two-byte HPI addressing. Dual firmware mode with two copies of firmware that can do mutual updates. |

|         |            |     | b6-b4: Flash row size                                                                                               |

|         |            |     | 0 – 128 bytes                                                                                                       |

|         |            |     | 1 – 256 bytes                                                                                                       |

|         |            |     | Other values reserved                                                                                               |

|         |            |     | b3-b2: Number of PD ports supported                                                                                 |

|         |            |     | 0 – 1 port                                                                                                          |

|         |            |     | 1 – 2 ports                                                                                                         |

|         |            |     | Other values reserved                                                                                               |

|         |            |     | b1-b0:                                                                                                              |

|         |            |     | 0 – Boot mode                                                                                                       |

|         |            |     | 1 – Firmware 1                                                                                                      |

|         |            |     | 2 – Firmware 2                                                                                                      |

**HPI Register Set**

#### 3.1.2 **BOOT\_MODE\_REASON**

This register specifies why the CCG3/4 device is in boot mode instead of normal operation mode, as described in Table 6. The EC can read this register to determine the reason for boot mode if CCG3/4 stays in boot mode for a long time. This register is available for access only in boot mode. It contains the value 0x00 in normal operation mode.

Table 6 **BOOT\_MODE\_REASON** Register

| BOOT_M  | BOOT_MODE_REASON: 1 Byte<br>CCG3/CCG4 Address: 0x0001 |     |                                                                                      |  |  |  |

|---------|-------------------------------------------------------|-----|--------------------------------------------------------------------------------------|--|--|--|

| CCG3/CC |                                                       |     |                                                                                      |  |  |  |

| Field   | Field<br>Name                                         | R/W | Description                                                                          |  |  |  |

| Byte 0  | Reason                                                | R   | b0 : Boot mode request by firmware                                                   |  |  |  |

|         |                                                       |     | 0 – No boot mode request                                                             |  |  |  |

|         |                                                       |     | 1 – Firmware switched to boot mode due to JUMP_TO_BOOT request.                      |  |  |  |

|         |                                                       |     | b1 : Configuration Table Status                                                      |  |  |  |

|         |                                                       |     | 0 – Table valid                                                                      |  |  |  |

|         |                                                       |     | 1 – Table invalid                                                                    |  |  |  |

|         |                                                       |     | Note: This bit is not used in CCG3/4 as the configuration table is part of firmware. |  |  |  |

|         |                                                       |     | b2: Firmware application 1 status                                                    |  |  |  |

|         |                                                       |     | 0: Application image valid                                                           |  |  |  |

|         |                                                       |     | 1: Application image invalid                                                         |  |  |  |

|         |                                                       |     | b3: Firmware application 2 status                                                    |  |  |  |

|         |                                                       |     | 0: Application image valid                                                           |  |  |  |

|         |                                                       |     | 1: Application image invalid                                                         |  |  |  |

|         |                                                       |     |                                                                                      |  |  |  |

#### 3.1.3 READ\_SILICON\_ID

This register contains the upper 2 bytes of the Silicon ID of the CCG3/4 device, as described in Table 7. It is available for access in both bootloader and normal firmware mode.

b4:b7: Reserved. This nibble is always 0.

Table 7 **READ\_SILICON\_ID Register**

| READ_SILICON_ID: 2 Bytes  |

|---------------------------|

| CCG3/CCG4 Address: 0x0002 |

| Field     | Field Name | R | Description                 |

|-----------|------------|---|-----------------------------|

| Byte[0:1] | Silicon ID | R | 2-byte Silicon ID of device |

|           |            |   |                             |

**HPI Register Set**

#### 3.1.4 **BOOT LOADER LAST ROW**

This register holds the index of the last flash row occupied by the bootloader, as described in **Table 8**. Each flash row of the CCG3/4 device contains 128 (for CCG3) or 256 (for CCG4) bytes, and the first flash row is indexed 0. This is a read-only register and is available only in boot mode.

Table 8 **BOOT\_LOADER\_LAST\_ROW Register**

**BOOT\_LOADER\_LAST\_ROW: 2 Bytes** CCG3/CCG4 Address: 0x0004 **Field Name Field Description** Byte[0:1] Last flash R Number of the last flash row occupied by bootloader row number

#### 3.1.5 INTR\_REG

If the CCG3/4 device needs attention, it drives the INTR# pin low and sets the bit 0,1 and 2 to 1, depending on whether the device and/or Type-C port 0/1 requires attention. The CCG3/4 device then expects the EC to service this interrupt. Once the EC has serviced the interrupt, the EC must clear the interrupt by writing 0 to this register, as described in Table 9. Once it is written, the CCG3/4 device drives the INTR# pin high assuming that there are no pending events for the EC to process.

If the CCG3/4 device has other events for the EC to process, this register cannot be cleared (and the INTR# line may not go back high). In such situations, the EC must read and process all remaining events until the INTR# line goes back high.

Table 9 **INTR\_REG Register**

INTO DEG. 1 Ryte

| IN I K_KE | INTR_REG: 1 Byte |               |                                                                                                                                |  |  |  |

|-----------|------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CCG3/CC   | G4 Address: 0>   | <b>k</b> 0006 |                                                                                                                                |  |  |  |

| Field     | Field Name       | R/W           | Description                                                                                                                    |  |  |  |